HP Superdome SX2000 User Service Guide, Seventh Edition - HP Integrity Superdo - Page 33

Memory Controller, DIMM Architecture, Memory Interconnect

|

View all HP Superdome SX2000 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 33 highlights

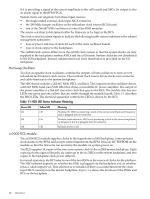

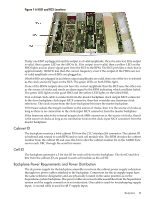

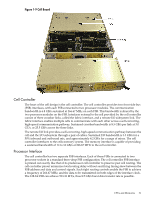

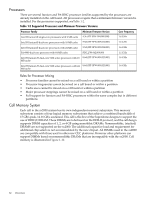

Figure 1-10 Cell Memory DIMMs are named according to both physical location and loading order. The physical location is used for connectivity on the board and is the same for all quads. Physical location is a letter (A or B) followed by a number (0, 1, 2, or 3). The letter indicates which side of the quad the DIMM is on. A is the left side, or the side nearest CC. The DIMMs are then numbered 0 through 3, starting at the outer DIMM and moving inwards the memory controllers. Memory Controller The memory controller CEC's primary function is to source address and control signals and multiplex and demultiplex data between the CC and the devices on the DDR DIMMs. Four independent memory blocks, consisting of two memory controllers and eight DIMMs, are supported by interface buses running between the CC and the memory controller. The memory controller converts these link streams to the correct signaling voltage levels (1.8 V) and timing for DDR2 protocol. Bandwidth is limited by the memory interface buses that transfer data between the CC and the memory controller. The memory controller also performs the write (tag update) portion of a read-modify-write (RMW) access. The memory controller is bit sliced, and two controllers are required to form one 72-bit CC memory interface data (MID) bus. The CC MID buses are bidirectional, source synchronous, and run at 533.33 MT/s. The memory side of a pair of memory controller ASICs consists of two 144-bit bidirectional DDR2 SDRAM data buses operating at 533.33 MT/s. Each bus supports up to four echelons of DRAMs. DIMM Architecture The fundamental building block of the DIMM is a DDR2 DRAM with a 4-bit data width. Each DIMM transfers 72 bits of data on a read/write, and the data is double-clocked at a clock frequency of 266.67 MHz for an effective peak transfer rate of 533.33 MT/s. Each DIMM includes 36 DRAM devices for data storage and two identical custom address buffers. These buffers fan out and check the parity of address and control signals received from the memory controller. The DIMM densities for the sx2000 are 1 GB (256 Gb DRAMs), 2 GB (512 Gb DRAMs), and 4 GB (1 Gb DRAMs). The new sx2000 chipset DIMMs have the same mechanical form factor as the DIMMs used in Integrity systems, but the DIMM and the connector, are keyed differently from previous DIMM designs to prevent improper installation. The DIMM is roughly twice the height of an industry-standard DIMM. This height increase enables the DIMM to accommodate twice as many DRAMs as an industry-standard DIMM and provides redundant address and control signal contacts not available on industry-standard DDR2 DIMMs. Memory Interconnect MID bus data is transmitted through the four 72-bit, ECC-protected MID buses, each with a clock frequency equal to the CC core frequency. The data is transmitted on both edges of the clock, so the data transfer rate (533 MT/s) of each MID is twice the MID clock frequency (267 MHz). A CPUs and Memories 33