Intel S1200BTL Product Specification - Page 149

Glossary - memory compatibility list

|

View all Intel S1200BTL manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 149 highlights

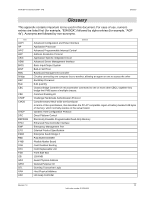

Intel®Server Board S1200BT TPS Glossary Glossary This appendix contains important terms used in this document. For ease of use, numeric entries are listed first (for example, ―82460GX‖) followed by alpha entries (for example, ―AGP 4x‖). Acronyms are followed by non-acronyms. Term ACPI AP APIC ARP ASIC ASMI BIOS BIST BMC Bridge BSP Byte CBC CEK CHAP CMOS DHCP DPC EEPROM EHCI EMP EPS ESB2 FBD F MB FRB FRU FSB GB GPA GPIO GTL HPA HSC Definition Advanced Configuration and Power Interface Application Processor Advanced Programmable Interrupt Control Address Resolution Protocol Application Specific Integrated Circuit Advanced Server Management Interface Basic Input/Output System Built-In Self Test Baseboard Management Controller Circuitry connecting one computer bus to another, allowing an agent on one to access the other Bootstrap Processor 8-bit quantity Chassis Bridge Controller (A microcontroller connected to one or more other CBCs, together they bridge the IPMB buses of multiple chassis. Common Enabling Kit Challenge Handshake Authentication Protocol Complementary Metal-oxide-semiconductor In terms of this specification, this describes the PC-AT compatible region of battery-backed 128 bytes of memory, which normally resides on the server board. Dynamic Host Configuration Protocol Direct Platform Control Electrically Erasable Programmable Read-Only Memory Enhanced Host Controller Interface Emergency Management Port External Product Specification Enterprise South Bridge 2 Fully Buffered DIMM Flexible Mother Board Fault Resilient Booting Field Replaceable Unit Front Side Bus 1024 MB Guest Physical Address General Purpose I/O Gunning Transceiver Logic Host Physical Address Hot-swap Controller Revision 1.0 137 Intel order number G13326-003