Intel S1200BTL Product Specification - Page 30

Memory Supported, Post Error Codes - two beeps then three beeps

|

View all Intel S1200BTL manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 30 highlights

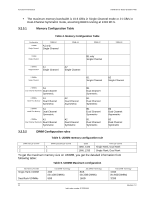

Functional Architecture Intel®Server Board S1200BT TPS The memory channels are named as ―Channel A‖ and ―Channel B‖. The memory slots are named as ―Slot1‖ and ―Slot2‖ on each channel. Slot1will be the farthest from the processor socket. DIMMs are named to reflect the channel and slot in which they are installed: o Channel A, Slot1 is ―DIMM_A1‖. o Channel A, Slot2 is ―DIMM_A2‖. o Channel B, Slot1 is ―DIMM_B1‖. o Channel B, Slot2 is ―DIMM_B2‖. 3.2.1 Memory Supported The Intel® Server Board S1200BT family supports various DDR3 DIMM modules of different types and sizes and speeds. In this section, the statements of support are subject to qualification in two ways: For S1200 Server Boards with an SNB-DT processor, the Server Board and the BIOS may support: DIMMs composed of Dynamic Random Access Memory (DRAM) chips using 1 Gb, 2 Gb, or 4 Gb technology DIMMs using x8 DRAM technology only DIMMs organized as Single Rank (SR) or Dual Rank (DR) DIMM sizes of 1 GB, 2 GB, 4 GB, or 8 GB DIMM speeds of 1066 or 1333 MT/s (megatransfers/second) Only Unregistered (Unbuffered) DIMMs (UDIMMs) are supported Only Error Correction Code (ECC) enabled DIMMs are supported UDIMMs may or may not have thermal sensors Note: UDIMMs must be ECC, and may or may not have thermal sensors. S1200BT BIOS has the following limitations: No support for LV DIMMs No support for RDIMMs All channels in a system will run at the fastest common frequency Mixing ECC and non-ECC UDIMMs anywhere on the platform is not supported Static Closed Loop Thermal Throttling (CLTT) supported via BMC (requires ECC DIMMs with thermal sensor) 3.2.2 Post Error Codes The range {0xE0 - 0xEF} of POST codes is used for memory errors in early POST. In late POST, this same range of POST code values is used for reporting other system errors. 0xE8 - No Usable Memory Error: If no usable memory is available, the BIOS emits a beep code and displays POST Diagnostic LED code 0xE8 and halts the system. 18 Revision 1.0 Intel order number G13326-003