Intel S1200BTL Product Specification - Page 37

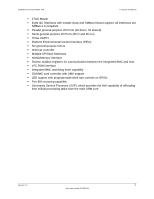

Parallel general-purpose I/O Ports 16 direct, 32 shared - processor support

|

View all Intel S1200BTL manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 37 highlights

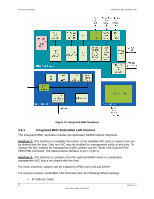

Intel®Server Board S1200BT TPS Functional Architecture JTAG Master Eight I2C interfaces with master-slave and SMBus timeout support. All interfaces are SMBus 2.0 compliant. Parallel general-purpose I/O Ports (16 direct, 32 shared) Serial general-purpose I/O Ports (80 in and 80 out) Three UARTs Platform Environmental Control Interface (PECI) Six general-purpose timers Interrupt controller Multiple SPI flash interfaces NAND/Memory interface Sixteen mailbox registers for communication between the Integrated BMC and host LPC ROM interface Integrated BMC watchdog timer capability SD/MMC card controller with DMA support LED support with programmable blink rate controls on GPIOs Port 80h snooping capability Secondary Service Processor (SSP), which provides the HW capability of offloading time critical processing tasks from the main ARM core. Revision 1.0 25 Intel order number G13326-003