Intel S1200BTL Product Specification - Page 33

Intel, Chipset PCH - error codes

|

View all Intel S1200BTL manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 33 highlights

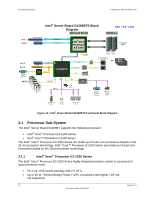

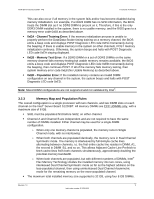

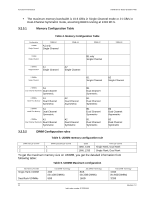

Intel®Server Board S1200BT TPS Functional Architecture Max Memory Possible 1Gb DRAM Technology (4x 2GB DIMMs) 2Gb DRAM Technology (4x 4GB DIMMs) 4Gb DRAM Technology (4x 8GB DIMMs) 3.2.4 Publishing System Memory For S1200 Server Boards with an SNB-DT processor, the memory configurations and population rules are relatively simple. The overall configuration is a single processor/IMC, with two channels, and two DIMM slots on each channel. All memory DIMMs are ECC UDIMMs only, with a maximum size of 8 GB. Slot1 must be populated first before Slot2, on either channel. Channel A and Channel B are independent and are not required to have the same number of DIMMs installed. Either channel may be used for a single-DIMM configuration. o When only one memory channel is populated, the memory runs in Single Channel mode, with no interleaving. 3.2.5 Memory RAS Support For Intel® Server Board S1200BT, the form of Memory RAS provided is Error Correction Code (ECC). ECC uses ―extra bits‖ - 64-bit data in a 72-bit DRAM array - to add an 8-bit calculated ―Hamming Code‖ to each 64 bits of data. This additional encoding enables the memory controller to detect and report single or double bit errors, and to correct single-bit errors. There is a specific step in memory initialization in which all of memory is cleared to zeroes before the ECC function is enabled, in order to bring the ECC codes into agreement with memory contents. During operation, in the process of every fetch from memory, the data and ECC bits are examined for each 64-bit data + 8-bit ECC group. If the ECC computation indicates that a single bit Correctable Error has occurred, it is corrected and the corrected data is passed on to the processor. If a double-bit Uncorrectable Error is detected, it cannot be corrected. In each case, a Correctable or Uncorrectable ECC Error event is generated. For Correctable Errors, there is a certain tolerance observed, since a Correctable Error can be generated by something as random as a stray Cosmic Ray impacting the DIMM. Correctable Errors are counted on a per-DIMM basis, but are just silently recorded until the tolerance threshold is crossed. The Correctable Error Threshold for Intel® Server Board S1200BT board is set at 10 events. When the 10th CE occurs, a single Correctable Error event is logged. 3.3 Intel® Chipset PCH The Intel® C200Series Chipset is designed for use with Intel® Xeon® Processor E3-1200 series or Intel® Core™ Processor i3-2100 in a UP server platform. The role of the PCH in the Intel® Server Board S1200BT is to manage the flow of information between its eleven interfaces, described below: DMI interface to Processor PCI Express* Interface PCI Interface Serial ATA Interface LPC Interface to IBMC and TPM Revision 1.0 21 Intel order number G13326-003