Intel S1200BTL Product Specification - Page 31

Memory Map and Population Rules - tested memory

|

View all Intel S1200BTL manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 31 highlights

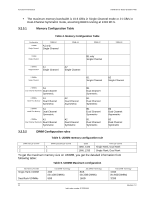

Intel®Server Board S1200BT TPS Functional Architecture This can also occur if all memory in the system fails and/or has become disabled during memory initialization. For example, if a DDR3 DIMM has no SPD information, the BIOS treats the DIMM slot as if no DDR3 DIMM is present on it. Therefore, if this is the only DDR3 DIMM installed in the system, there is no usable memory, and the BIOS goes to a memory error code 0xE8 as described above. 0xEA - Channel Training Error: If the memory initialization process is unable to properly perform the Data/Data Strobe timing training on a memory channel, the BIOS emits a beep code and displays POST Diagnostic LED code 0xEA momentarily during the beeping. If there is usable memory in the system on other channels, POST memory initialization continues. Otherwise, the system beeps and halts with POST Diagnostic LED code 0xEA staying displayed. 0xEB - Memory Test Error: If a DDR3 DIMM or a set of DDR3 DIMMs on the same memory channel fails memory testing but usable memory remains available, the BIOS emits a beep code and displays POST Diagnostic LED code 0xEB momentarily during the beeping, then continues POST. If all of the memory fails memory testing, then system memory error code 0xE8 (No Usable Memory) as described above. 0xED - Population Error: If the installed memory contains an invalid DIMM configuration on any channel in the system, the system beeps and halts with POST Diagnostic LED code 0xED. Note: Mixed DIMM configurations are not supported and not validated by Intel®. 3.2.3 Memory Map and Population Rules The overall configuration is a single processor with two channels, and two DIMM slots on each channel on the Intel® Server Board S1200BT. All memory DIMMs are ECC UDIMMs only, with a maximum size of 8 GB. Slot1 must be populated first before Slot2, on either channel. Channel A and Channel B are independent and are not required to have the same number of DIMMs installed. Either channel may be used for a single-DIMM configuration. o When only one memory channel is populated, the memory runs in Single Channel mode, with no interleaving. o When both channels are populated identically, the memory runs in Dual Channel Symmetric mode. The memory is interleaved by full 64-byte cache lines alternating between channels, i.e. the first entire cache line resides in DIMM_A1, the second in DIMM_B1, and so on. This allows Adjacent Cache Line Prefetch to fetch cache lines from both channels simultaneously, approximately doubling the potential memory bandwidth. o When both channels are populated, but with different numbers of DIMMs, Intel® Flex Memory Technology divides the installed memory into two zones, using interleaved Dual Channel Symmetric mode as far as the highest address on the less-populated channel, then using uninterleaved Dual Channel Asymmetric mode for the remaining memory on the more-populated channel. The maximum total installed memory size supported is 32 GB, using four 8 GB DIMMs. Revision 1.0 19 Intel order number G13326-003