Intel S1200BTL Product Specification - Page 35

Low Pin Count LPC Interface, USB 2.0 Support - compatible memory

|

View all Intel S1200BTL manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 35 highlights

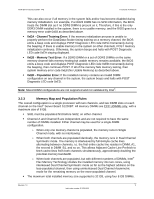

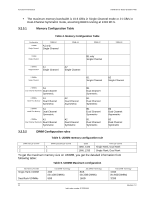

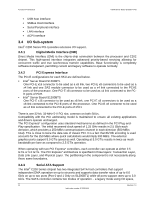

Intel®Server Board S1200BT TPS Functional Architecture and an AHCI mode using memory space. Software that uses legacy mode will not have AHCI capabilities. Software that uses legacy mode does not have Advanced Host Configuration Interface (AHCI) capabilities. The Intel® C202 PCH Chipset supports the Serial ATA Specification, Revision 1.0a. The PCH also supports several optional sections of the Serial ATA II: Extensions to Serial ATA 1.0 Specification, Revision 1.0 (AHCI support is required for some elements). The Intel® C200 Series chipset PCH provides hardware support for AHCI, a standardized programming interface for SATA host controllers. Platforms supporting AHCI may take advantage of performance features such as no master/slave designation for SATA devices- each device is treated as a master - and hardware assisted native command queuing. AHCI also provides usability enhancements such as Hot-Plug. AHCI requires appropriate software support (e.g., an AHCI driver) and for some features, hardware support in the SATA device or additional platform hardware. 3.4.3.1 Intel® Matrix Storage Technology The Intel® C200 Series chipset provides support for Intel® Rapid Storage Technology, providing both AHCI (see above for details on AHCI) and integrated RAID functionality. The RAID capability provides high-performance RAID 0, 1, 5, and 10 functionality on up to 6 SATA ports of the PCH. Matrix RAID support is provided to allow multiple RAID levels to be combined on a single set of hard drives, such as RAID 0 and RAID 1 on two disks. Other RAID features include hot spare support, SMART alerting, and RAID 0 auto replace. Software components include an Option ROM for pre-boot configuration and boot functionality, a Microsoft Windows* compatible driver, and a user interface for configuration and management of the RAID capability of PCH. 3.4.4 Low Pin Count (LPC) Interface The Intel® C200 Series chipset implements an LPC Interface as described in the LPC 1.1 Specification. The Low Pin Count (LPC) bridge function of the C202 resides in PCI Device 31: Function 0. In addition to the LPC bridge interface function, D31:F0 contains other functional units including DMA, interrupt controllers, timers, power management, system management, GPIO, and RTC. 3.4.5 USB 2.0 Support On the Intel® C200 series PCH Chipset, the USB controller functionality is provided by the dual EHCI controllers with an interface for up to ten USB 2.0 ports. All ports are high-speed, full- speed, and low-speed capable. Four external connectors are located on the back edge of the server board. Two internal 2x5 headers (J1E1 and J1D1) are provided, each supporting two optional USB 2.0 ports. One port on internal smart module connector (J1J2) on Intel® Server Board S1200BTL. 3.4.5.1 Native USB Support During the power-on self test (POST), the BIOS initializes and configures the USB subsystem. The BIOS is capable of initializing and using the following types of USB devices. Revision 1.0 23 Intel order number G13326-003