HP Dc7700 HP Compaq dx7300 and dc7700 Business PC Technical Reference Guide, 1 - Page 47

instructions dealing with branching sequences that are checked when re-occurring branches are - cpu support

|

UPC - 882780715318

View all HP Dc7700 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 47 highlights

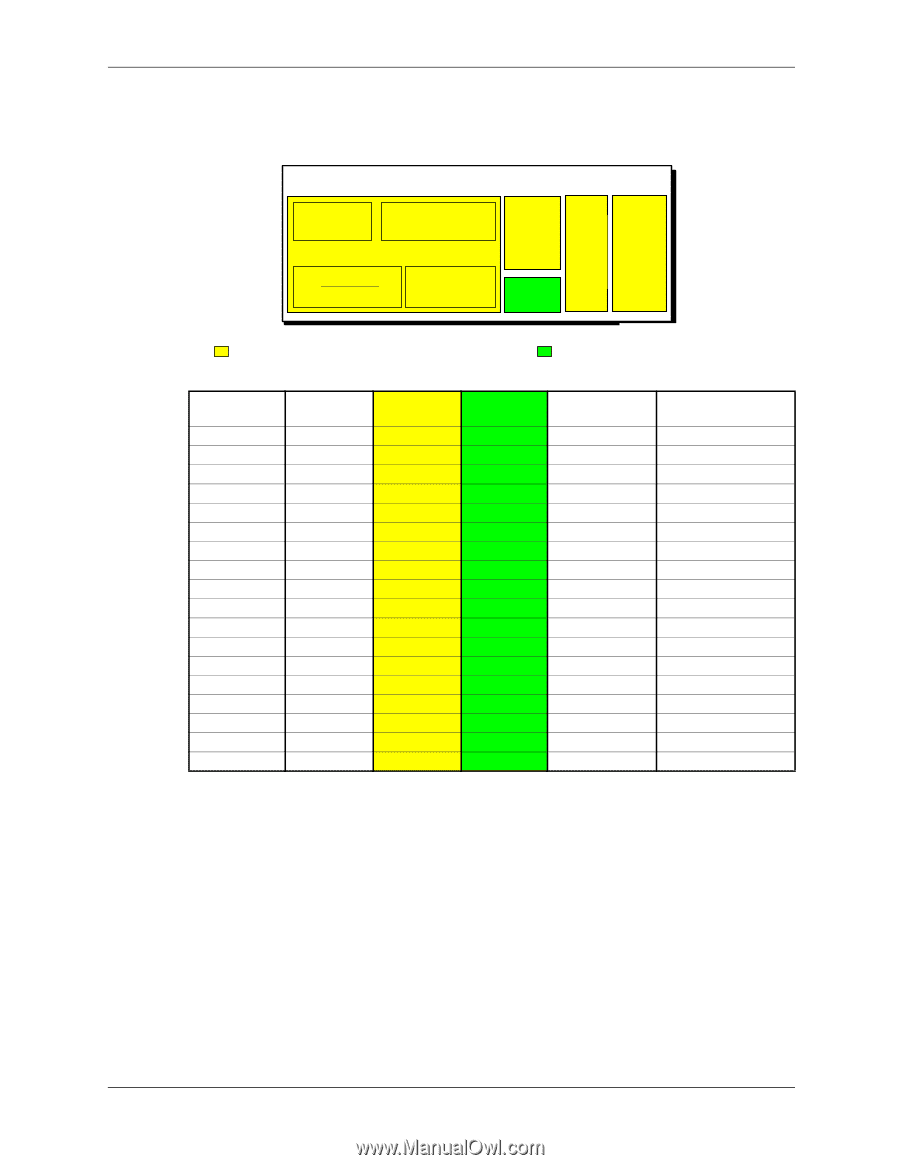

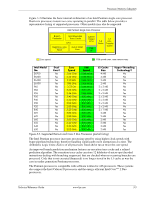

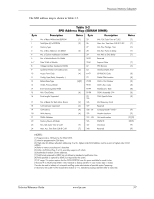

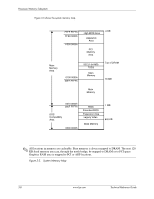

Processor/Memory Subsystem Figure 3-2 illustrates the basic internal architecture of an Intel Pentium single-core processor. Dual-core processors feature two cores operating in parallel. The table below provides a representative listing of supported processors. Other models may also be supported. Intel PPeenntituiummS4inPgrloecCesosreorProcessor Branch Prediction 16-K Execution Trace Cache CPU Rapid Exe. Eng. AALLUUss Out-of-Order Core 128-bit Integer FPU FSB I/F 8-K LL11 CDaacthae Cache L2 Adv.. Transfer Cache Core speed ALU Speed (Core speed x2) FSB speed (max. data transfer rate) Intel Model No. E6700 E6600 E6400 E6300 965 960 955 950 940 930 920 840 672 670 660 650 640 630 Dual Core? Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes Yes No No No No No No Core Speed 2.66 GHz 2.40 GHz 2.13 GHz 1.86 GHz 3.73 GH 3.60 GHz 3.46 GHz 3.40 GHz 3.20 GHz 3.00 GHz 2.80 GHz 3.20 GHz 3.80 GHz 3.80 GHz 3.60 GHz 3.40 GHz 3.20 GHz 3.00 GHz FSB Speed 1066 MHz 1066 MHz 1066 MHz 1066 MHz 1066 MHz 800 MHz 1066 MHz 800 MHz 800 MHz 800 MHz 800 MHz 800 MHz 800 MHz 800 MHz 800 MHz 800 MHz 800 MHz 800 MHz L2 Cache Size 4 MB 4 MB 2 MB 2 MB 2 x 2 MB 2 x 2 MB 2 x 2 MB 2 x 2 MB 2 x 2 MB 2 x 2 MB 2 x 2 MB 2 x 1 MB 2 MB 2 MB 2 MB 2 MB 2 MB 2 MB Hyper-Threading Technology? No No No No Yes No Yes No No No No No Yes Yes Yes Yes Yes Yes Figure 3-2. Supported Pentium and Core 2 Duo Processors (partial listing) The Intel Pentium processor increases processing speed by using higher clock speeds with hyper-pipelined technology, therefore handling significantly more instructions at a time. The Arithmetic Logic Units (ALUs) of all processors listed above run at twice the core speed. An improved branch prediction mechanism features an execution trace cache and a refined prediction algorithm. The execution trace cache can store 12 kilobytes of micro-ops (decoded instructions dealing with branching sequences) that are checked when re-occurring branches are processed. Code that is not executed (bypassed) is no longer stored in the L1 cache as was the case in earlier generation Pentium processors. The Pentium processor is compatible with software written for x86 processors. These systems also support the Intel Celeron D processors and the energy-efficient Intel CoreT M 2 Duo processors. Technical Reference Guide www.hp.com 3-3