HP Dc7700 HP Compaq dx7300 and dc7700 Business PC Technical Reference Guide, 1 - Page 60

Option ROM Mapping, 4.2.4 PCI Interrupts, 4.2.5 PCI Power Management Support, The SFF, ST, MT - graphics driver

|

UPC - 882780715318

View all HP Dc7700 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 60 highlights

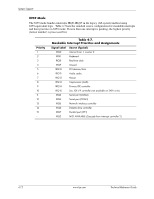

System Support For a PCI Express x16 transfer, a lane will be re-used for the transfer of every17th byte. The mux-demux process provided by the physical layer is transparent to the other layers and to software/drivers. The SFF, ST, MT, and CMT form factors provide two PCI Express slots: a PCI Express x16 (16-lane) slot specifically designed for a graphics controller, and a general purpose PCI Express x1 (1-lane) slot. 4.2.3 Option ROM Mapping During POST, the PCI bus is scanned for devices that contain their own specific firmware in ROM. Such option ROM data, if detected, is loaded into system memory's DOS compatibility area (refer to the system memory map shown in chapter 3). 4.2.4 PCI Interrupts Eight interrupt signals (INTA- thru INTH-) are available for use by PCI devices. These signals may be generated by on-board PCI devices or by devices installed in the PCI slots. For more information on interrupts including PCI interrupt mapping refer to the "System Resources" section 4.3. 4.2.5 PCI Power Management Support This system complies with the PCI Power Management Interface Specification (rev 1.0). The PCI Power Management Enable (PME-) signal is supported by the chipset and allows compliant PCI peripherals to initiate the power management routine. 4-8 www.hp.com Technical Reference Guide