HP Dc7700 HP Compaq dx7300 and dc7700 Business PC Technical Reference Guide, 1 - Page 76

Register Map and Miscellaneous Functions, 4.6.1 System I/O Map

|

UPC - 882780715318

View all HP Dc7700 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 76 highlights

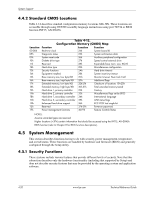

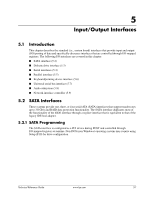

System Support 4.6 Register Map and Miscellaneous Functions This section contains the system I/O map and information on general-purpose functions of the ICH8 and I/O controller. 4.6.1 System I/O Map Table 4-14 lists the fixed addresses of the input/output (I/O) ports. I/O Port 0000..001Fh 0020..002Dh 002E, 002Fh 0030..003Dh 0040..0042h 004E, 004Fh 0050..0052h 0060..0067h 0070..0077h 0080..0091h 0092h 0093..009Fh 00A0..00B1h 00B2h, 00B3h 00B4..00BDh 00C0..00DFh 00F0h 0170..0177h 01F0..01F7h 0278..027Fh 02E8..02EFh 02F8..02FFh 0370..0377h 0376h 0378..037Fh 03B0..03DFh 03BC..03BEh 03E8..03EFh 03F0..03F5h 03F6h 03F8..03FFh 04D0, 04D1h 0678..067Fh 0778..077Fh 07BC..07BEh 0CF8h 0CF9h 0CFCh Table 4-14 System I/O Map Function DMA Controller 1 Interrupt Controller 1 Index, Data Ports to SCH5317 I/O Controller (primary) Interrupt Controller Timer 1 Index, Data Ports to SCH5317 I/O Controller (secondary) Timer / Counter Microcontroller, NMI Controller (alternating addresses) RTC Controller DMA Controller Port A, Fast A20/Reset Generator DMA Controller Interrupt Controller 2 APM Control/Status Ports Interrupt Controller DMA Controller 2 Coprocessor error register IDE Controller 2 (active only if standard I/O space is enabled for secondary controller) IDE Controller 1 (active only if standard I/O space is enabled for primary controller) Parallel Port (LPT2) Serial Port (COM4) Serial Port (COM2) Diskette Drive Controller Secondary Address IDE Controller 2 (active only if standard I/O space is enabled for primary drive) Parallel Port (LPT1) Graphics Controller Parallel Port (LPT3) Serial Port (COM3) Diskette Drive Controller Primary Addresses IDE Controller 1 (active only if standard I/O space is enabled for sec. drive) Serial Port (COM1) Interrupt Controller Parallel Port (LPT2) Parallel Port (LPT1) Parallel Port (LPT3) PCI Configuration Address (dword access only ) Reset Control Register PCI Configuration Data (byte, word, or dword access) NOTE: Assume unmarked gaps are unused, reserved, or used by functions that employ variable I/O address mapping. Some ranges may include reserved addresses. 4-24 www.hp.com Technical Reference Guide