HP Dc7700 HP Compaq dx7300 and dc7700 Business PC Technical Reference Guide, 1 - Page 63

System Resources, 4.3.1 Interrupts

|

UPC - 882780715318

View all HP Dc7700 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 63 highlights

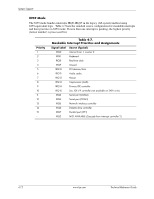

System Support 4.3 System Resources This section describes the availability and basic control of major subsystems, otherwise known as resource allocation or simply "system resources." System resources are provided on a priority basis through hardware interrupts and DMA requests and grants. 4.3.1 Interrupts The microprocessor uses two types of hardware interrupts; maskable and nonmaskable. A maskable interrupt can be enabled or disabled within the microprocessor by the use of the STI and CLI instructions. A nonmaskable interrupt cannot be masked off within the microprocessor, although it may be inhibited by hardware or software means external to the microprocessor. Maskable Interrupts The maskable interrupt is a hardware-generated signal used by peripheral functions within the system to get the attention of the microprocessor. Peripheral functions produce a unique INTA-H (PCI) or IRQ0-15 (ISA) signal that is routed to interrupt processing logic that asserts the interrupt (INTR-) input to the microprocessor. The microprocessor halts execution to determine the source of the interrupt and then services the peripheral as appropriate. Most IRQs are routed through the I/O controller of the super I/O component, which provides the serializing function. A serialized interrupt stream is then routed to the ICH component. Interrupts may be processed in one of two modes (selectable through the F10 Setup utility): ■ 8259 mode ■ APIC mode These modes are described in the following subsections. Technical Reference Guide www.hp.com 4-11