HP Dc7700 HP Compaq dx7300 and dc7700 Business PC Technical Reference Guide, 1 - Page 57

PCI 2.3 Bus Master Arbitration, function of the system controller component. If the bus is available - memory limit

|

UPC - 882780715318

View all HP Dc7700 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 57 highlights

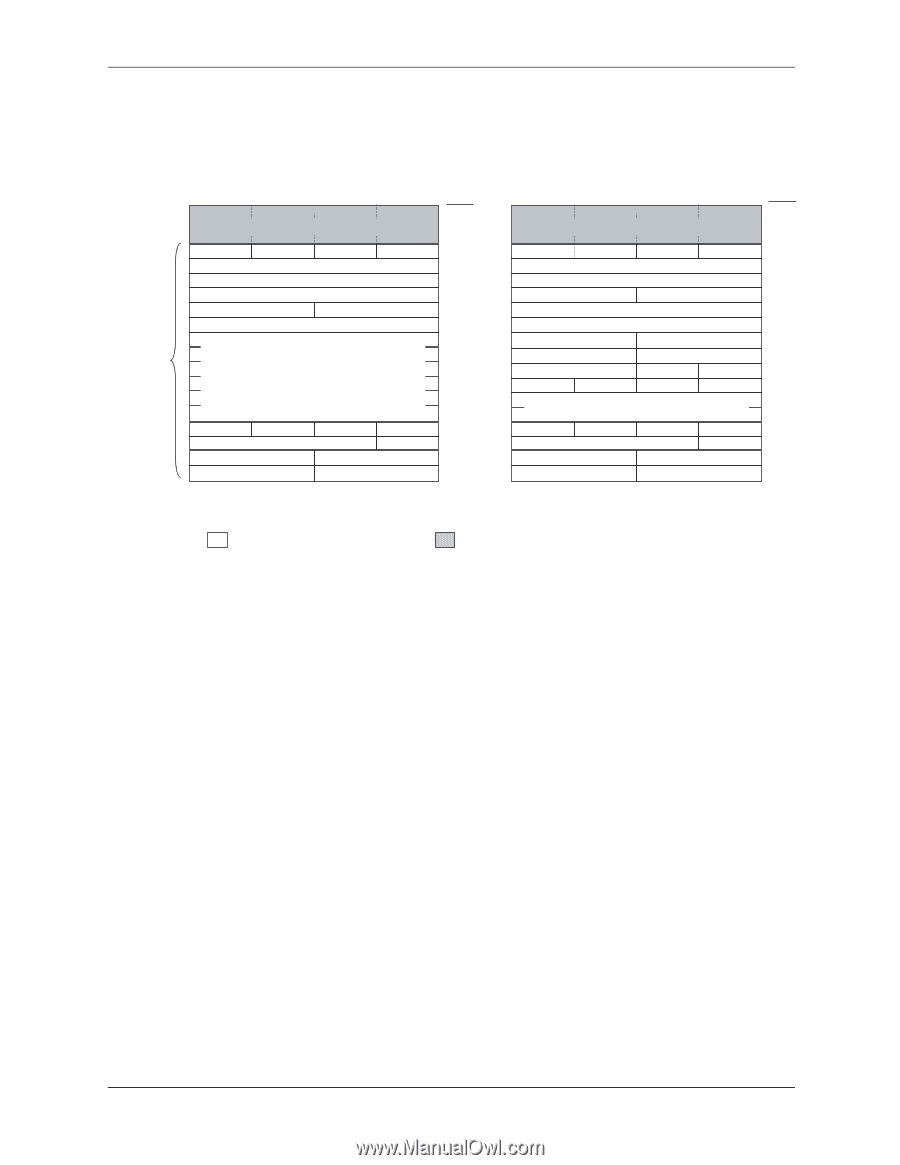

System Support The register index (CF8h, bits ) identifies the 32-bit location within the configuration space of the PCI device to be accessed. All PCI devices can contain up to 256 bytes of configuration data (Figure 4-3), of which the first 64 bytes comprise the configuration space header. Configuration Space Header 31 24 23 16 15 8 7 0 Device-Specific Area Min. Lat. Min. GNT Int. Pin Int. Line Reserved Reserved Ex pansion ROM Base Address Subs ystem ID Subs ystem Vendor ID Card Bus CIS Pointer Base Address Registers Index FCh 40h 3Ch 38h 34h 30h 2Ch 28h 10h BIST Hdr. T ype Lat. Timer Line Size 0Ch Class Code Status Revision ID 08h Command 04h Device ID Vendor ID 00h 31 24 23 16 15 8 7 0 Device-Specific Area Brid ge Control Int. Pin Int. Line Ex pansion ROM Base Address Reserved I/O Limit Upper 16 Bits I/O Base U pper 16 Bits Prefetchable Limit U pper 32 Bits Prefetchable Base U pper 32 Bits Prefetch. Mem. Limit Prefetch. Mem. Base Memory Limit Memory Base Secondar y Status I/O Limit I/O Base 2nd Lat.Tmr Sub. Bus # Sec. Bus # Pri. Bus # Base Address Registers BIST Hdr. T ype Class Code Status Device ID Lat. Timer Line Size Revision ID Command Vendor ID Index FCh 40h 3Ch 38h 34h 30h 2Ch 28h 24h 20h 1Ch 18h 10h 0Ch 08h 04h 00h PCI Configuration Space Type 0 PCI Configuration Space Type 1 Data required by PCI protocol Not required Figure 4-3. PCI Configuration Space Mapping PCI 2.3 Bus Master Arbitration The PCI bus supports a bus master/target arbitration scheme. A bus master is a device that has been granted control of the bus for the purpose of initiating a transaction. A target is a device that is the recipient of a transaction. The Request (REQ), Grant (GNT), and FRAME signals are used by PCI bus masters for gaining access to the PCI bus. When a PCI device needs access to the PCI bus (and does not already own it), the PCI device asserts it's REQn signal to the PCI bus arbiter (a function of the system controller component). If the bus is available, the arbiter asserts the GNTn signal to the requesting device, which then asserts FRAME and conducts the address phase of the transaction with a target. If the PCI device already owns the bus, a request is not needed and the device can simply assert FRAME and conduct the transaction. Table 4-3 shows the grant and request signals assignments for the devices on the PCI bus. Technical Reference Guide www.hp.com 4-5