HP Dc7700 HP Compaq dx7300 and dc7700 Business PC Technical Reference Guide, 1 - Page 54

PCI 2.3 Bus Operation, I/O and Memory Cycles

|

UPC - 882780715318

View all HP Dc7700 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 54 highlights

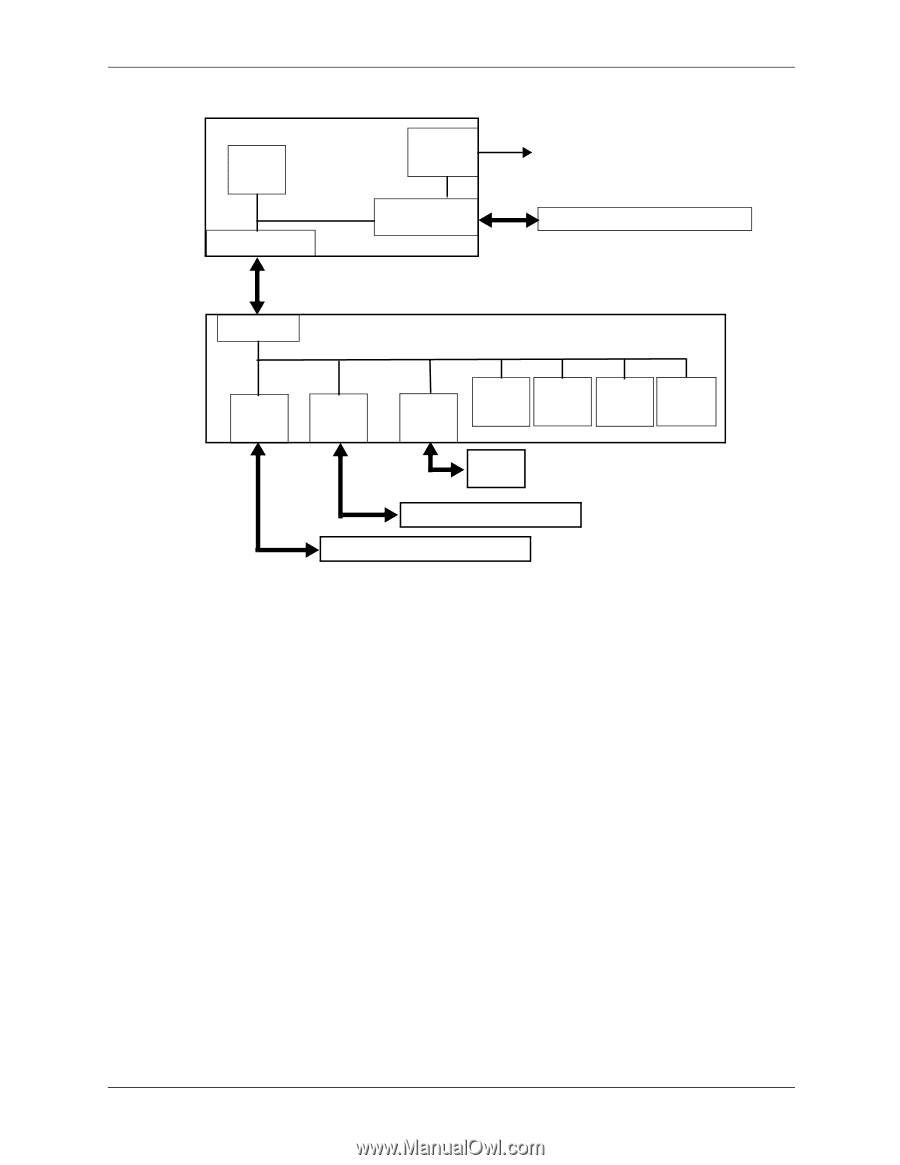

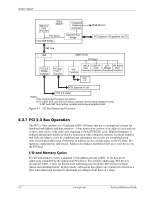

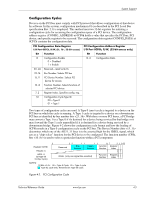

System Support Memory Cntlr Function Q965 GMCH PCI Bus 0 Host-DMI Bridge Integrated Graphics Controller Host-PCI Exp. Bridge RGB Monitor PCI Express x16 graphics slot [1] DMI Link DMI PCI 2.3 Bridge Function PCI Exp. Port 1 Function 82801 ICH8 PCI Bus 1 NIC. Function SATA USB I/F LPC HD Audio Cntlr Cntlr Bridge Cntlr Function Function Function Function NIC I/F PCI Express x1 slot PCI 2.3 slot(s) Notes: Only implemented functions are shown. [1] In USDT SFF, and ST form factors, accepts reverse-layout graphics cards. In MT and CMT form factors, accepts nomal layout graphics card. Figure 4-1. PCI Bus Devices and Functions 4.2.1 PCI 2.3 Bus Operation The PCI 2.3 bus consists of a 32-bit path (AD31-00 lines) that uses a multiplexed scheme for handling both address and data transfers. A bus transaction consists of an address cycle and one or more data cycles, with each cycle requiring a clock (PCICLK) cycle. High performance is realized during burst modes in which a transaction with contiguous memory locations requires that only one address cycle be conducted and subsequent data cycles are completed using auto-incremented addressing. Four types of address cycles can take place on the PCI bus; I/O, memory, configuration, and special. Address decoding is distributed (left up to each device on the PCI bus). I/O and Memory Cycles For I/O and memory cycles, a standard 32-bit address decode (AD31..0) for byte-level addressing is handled by the appropriate PCI device. For memory addressing, PCI devices decode the AD31..2 lines for dword-level addressing and check the AD1,0 lines for burst (linear-incrementing) mode. In burst mode, subsequent data phases are conducted a dword at a time with addressing assumed to increment accordingly (four bytes at a time). 4-2 www.hp.com Technical Reference Guide