HP Dc7700 HP Compaq dx7300 and dc7700 Business PC Technical Reference Guide, 1 - Page 53

Chap_4_System_Support_final_review.pdf, System Support, 4.1 Introduction, 4.2 PCI Bus Overview

|

UPC - 882780715318

View all HP Dc7700 manuals

Add to My Manuals

Save this manual to your list of manuals |

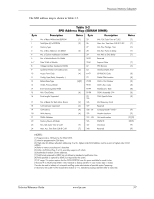

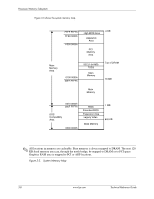

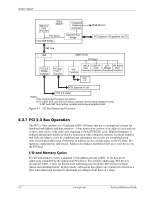

Page 53 highlights

4 System Support 4.1 Introduction This chapter covers subjects dealing with basic system architecture and covers the following topics: ■ PCI bus overview (4.2), page 4-1 ■ System resources (4.3), page 4-11 ■ Real-time clock and configuration memory (4.4), page 4-19 ■ System management (4.5), page 4-20 ■ Register map and miscellaneous functions (4.6), page 4-24 This chapter covers functions provided by off-the-shelf chipsets and therefore describes only basic aspects of these functions as well as information unique to the systems covered in this guide. For detailed information on specific components, refer to the applicable manufacturer's documentation. 4.2 PCI Bus Overview ✎ This section describes the PCI bus in general and highlights bus implementation in this particular system. For detailed information regarding PCI bus operation, refer to the appropriate PCI specification or the PCI web site: www.pcisig.com. These systems implement the following types of PCI buses: ■ PCI 2.3 - Legacy parallel interface operating at 33-MHz ■ PCI Express - High-performance interface capable of using multiple TX/RX high-speed lanes of serial data streams The PCI bus handles address/data transfers through the identification of devices and functions on the bus. A device is typically defined as a component or slot that resides on the PCI bus (although some components such as the GMCH and ICH8 are organized as multiple devices). A function is defined as the end source or target of the bus transaction. A device may contain one or more functions. In the standard configuration these systems use a hierarchy of three PCI buses (Figure 4-1). The PCI bus #0 is internal to the chipset components and is not physically accessible. The Direct Media Interface (DMI) links the GMCH and ICH8 components and operates as a subset of the PCI bus. All PCI slots and the NIC function internal to the ICH8 reside on PCI bus #2. Technical Reference Guide www.hp.com 4-1