Toshiba M200-ST2002 Maintenance Manual - Page 62

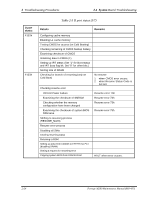

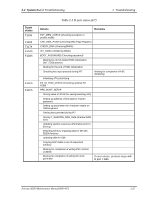

Troubleshooting Procedures, Board Troubleshooting, Table 2-3 D port status 3/7

|

View all Toshiba M200-ST2002 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 62 highlights

2 Troubleshooting Procedures 2.4 System Board Troubleshooting D port statu s F102h F103h Table 2-3 D port status (3/7) Details Remarks Configuring cache memory Enabling L1 cache memory Testing CMOS for access (on Cold Booting) Checking remaining of CMOS backup battery Examining checksum of CMOS Initializing data in CMOS (1) Setting up IRT status (Set "1" for Boot status and IRT busy flag bit. Set "0" for other bits.) Storing size of DRAM Checking for branch of resuming (only on Cold Boot) Checking resume error ICH4-M Power Failure Examining the checksum of SMRAM Checking whether the memory configuration have been changed Examining the checksum of system BIOS RAM area Shifting to resuming process (RESUME_MAIN) Resume error process Disabling all SMIs Clearing resuming status Returning to ROM Setting up area from C0000h to EFFFFh for PCI (disabling DRAM) Setting a request for resuming error Copying system BIOS from ROM to RAM No resume 1. when CMOS error occurs. 2. when Resume Status Code is not set. Resume error 7Ah Resume error 73h Resume error 73h Resume error 79h HALT when error occurs. 2-24 Portege M200 Maintenance Manual (960-457)