Epson LQ 1050 Technical Manual - Page 191

LPD781, Sginal

|

View all Epson LQ 1050 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 191 highlights

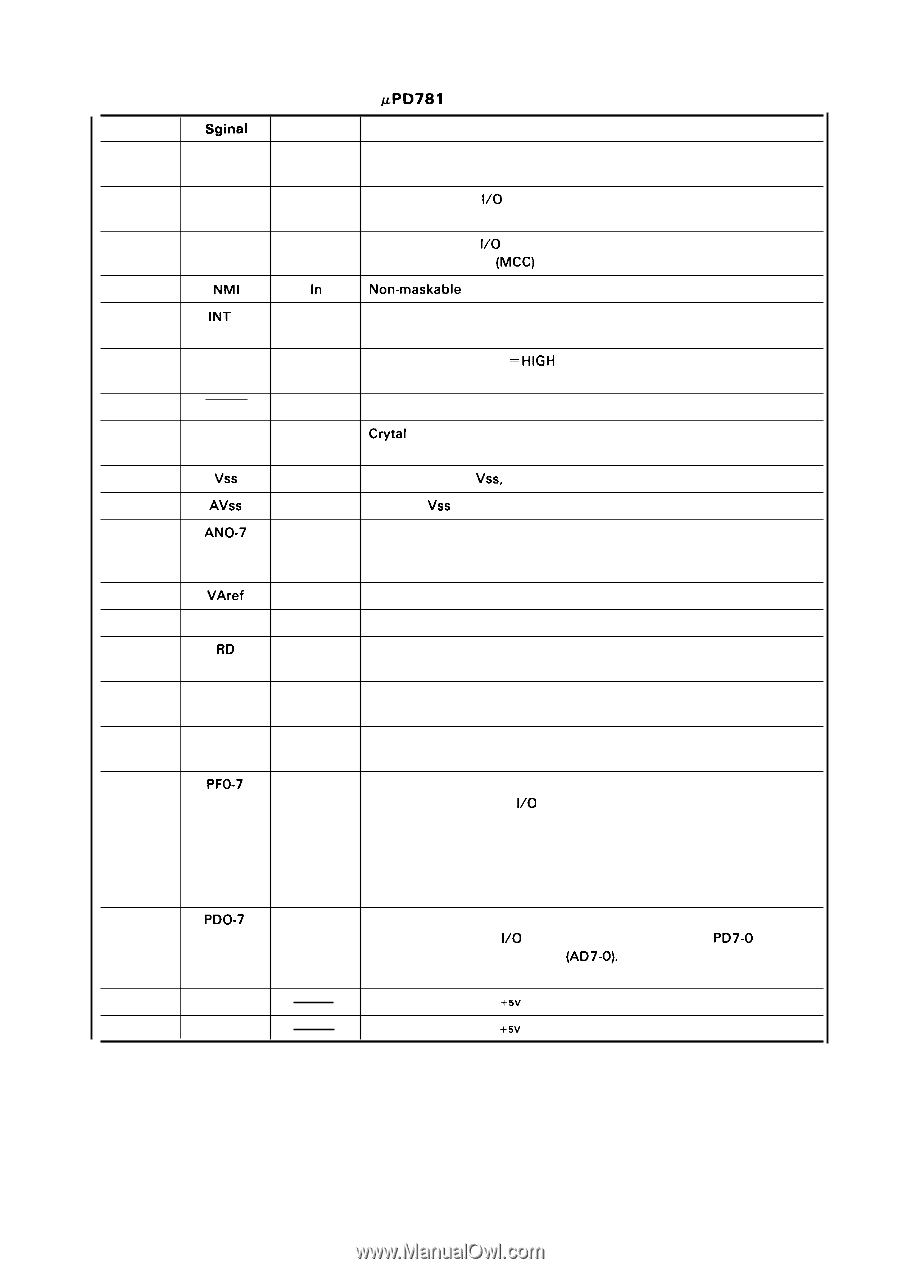

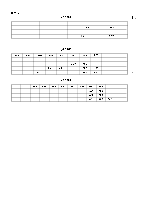

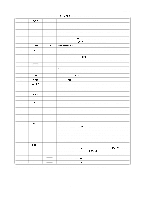

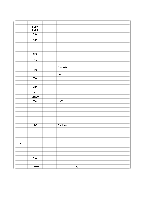

REV.-A Table A-6. 1.LPD781 0/781 1 Port Functions Pin Sginal Direction Descriptions 1-8 PAO-7 In/Out Port A: Eight-bit l/O with output latch. l/O possible by mode A (MA) register. Output HIGH. 9-16 17-24 25 26 27, 29 PBO-7 PCO-7 NMI INT 1 MODE 1,0 In/Out In/Out In In In/Out Port B: Eight-bit 1/0 with output latch. l/O possible by mode B (MB) register. Output HIGH. Port C: Eight-bit 1/0 with output latch. Port/Control mode can be set by mode control C (MCC) register. Output HIGH Non-maskable interrupt of the edge trigger (trailing edge). Maskable interrupt input of the edge trigger (leading edge). Also used as the AC input zero cross detecting terminal. 7811 :O=LOW and 1 =HIGH 7810 modes set in accordance with external memory (see Table A-2) 28 30, 31 32 33 34-41 42 43 44 45 46 47-54 55-62 63 64 RESET X2,X1 Vss AVSS ANO-7 VAref AVCC RD WR ALE PFO-7 PDO-7 VDD Vcc In - - - In In - out out out LOW reset Crytal connection for built-in clock pulse. When clock pulses are supplied externally, input must be to X 1. Supply voltage, Vss, OV Analong Vss Eight analog inputs of the A/D converter. AN7-4 can be used as the input terminals to the detect the leading edge and to set the test flag upon detection of the trailing edge. Reference voltage Analog Vcc Read strobe. LOW at the read machine cycle and at reset, HIGH at other times. Write strobe. LOW during the write machine cycle and at reset, HIGH at other times. Address latch enable. Latches the lower 8 address bits to access external memory. Port F 78: 1 1: Port bit-by-bit 1/0 possible by mode F register. In extension mode gradual address output assignment is possible in accordance with the size of external memory. See Table A-3. 78 10: By setting modes O and 1, assignment to the address bus (AB 15-8) can be made in accordance with the size of the external memory. The remaining terminals can be used as l/O ports. See Table A-4. Port D 781 1: Port bit-by-bit 1/0 possible. In extension mode, PD7-O act as the multiplexed address/data but (AD7-0). 78 10: Multiplexed address/data bus to access external memory. Supply voltage, VDD +5v Supply voltage, Vcc +5v NOTE: "Direction" refers to the direction of signal flow as viewed from the CPU. A-5