Epson LQ 1050 Technical Manual - Page 78

Computer

|

View all Epson LQ 1050 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 78 highlights

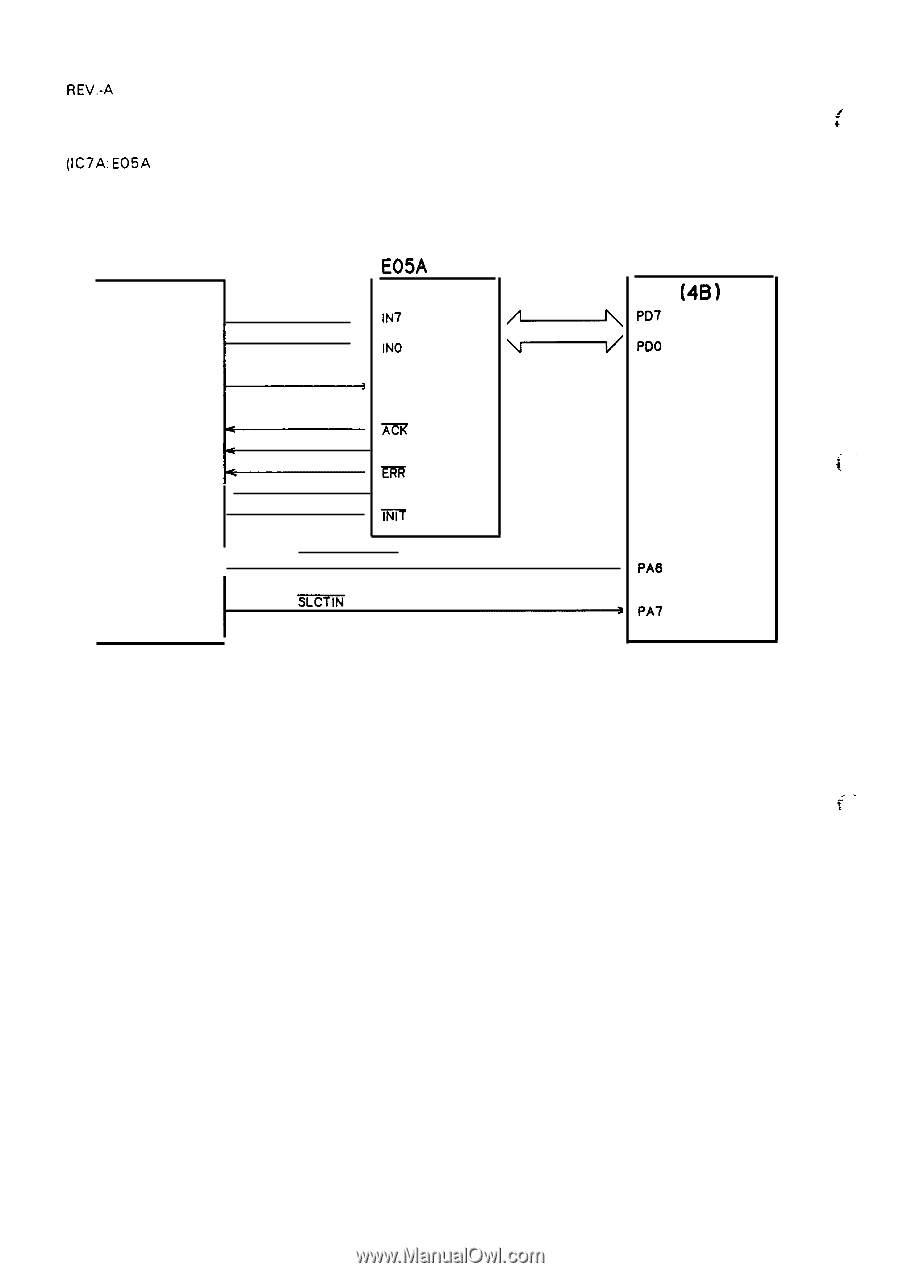

REV.-A 2.3.4.2 Interface Control Circuit ,y + Parallel data communication between the printer and host computer is controlled by the gate array (IC7A: E05A 16GA) on the PEGX board. Figure 2-28 shows the interface control circuit block diagram. Figure 2-29 shows the parallel interface data transmission timing. GA E05A 16 GA) (7A) IN7 D7 I DATA BUS ' I INO I DO HOST COMPUTER STROBE 1= m BUSY m PE m I AUTO FEED XT CPU (78 10HG) (4B) PD7 I PDO ,. i, 3 PA6 PA7 Figure 2-28. Interface Control Circuit Block Diagram ,. . $" 2-34

REV.-A

2.3.4.2 Interface Control Circuit

,y

Parallel data communication between the printer and host computer is controlled by the gate array

+

(IC7A:

E05A

16GA)

on the PEGX board. Figure 2-28 shows the interface control circuit block diagram.

Figure 2-29 shows the parallel interface data transmission timing.

I

DATA

BUS

‘

HOST

COMPUTER

1=

GA

E05A

16 GA)

(7A)

IN7

D7

I

I

INO

DO

STROBE

m

BUSY

m

PE

m

I

AUTO FEED XT

3

CPU

(78 10HG)

(4B)

PD7

I

PDO

PA6

PA7

Figure 2-28. Interface Control Circuit Block Diagram

,.

i,

,.

.

$“

2-34