Epson LQ 1050 Technical Manual - Page 204

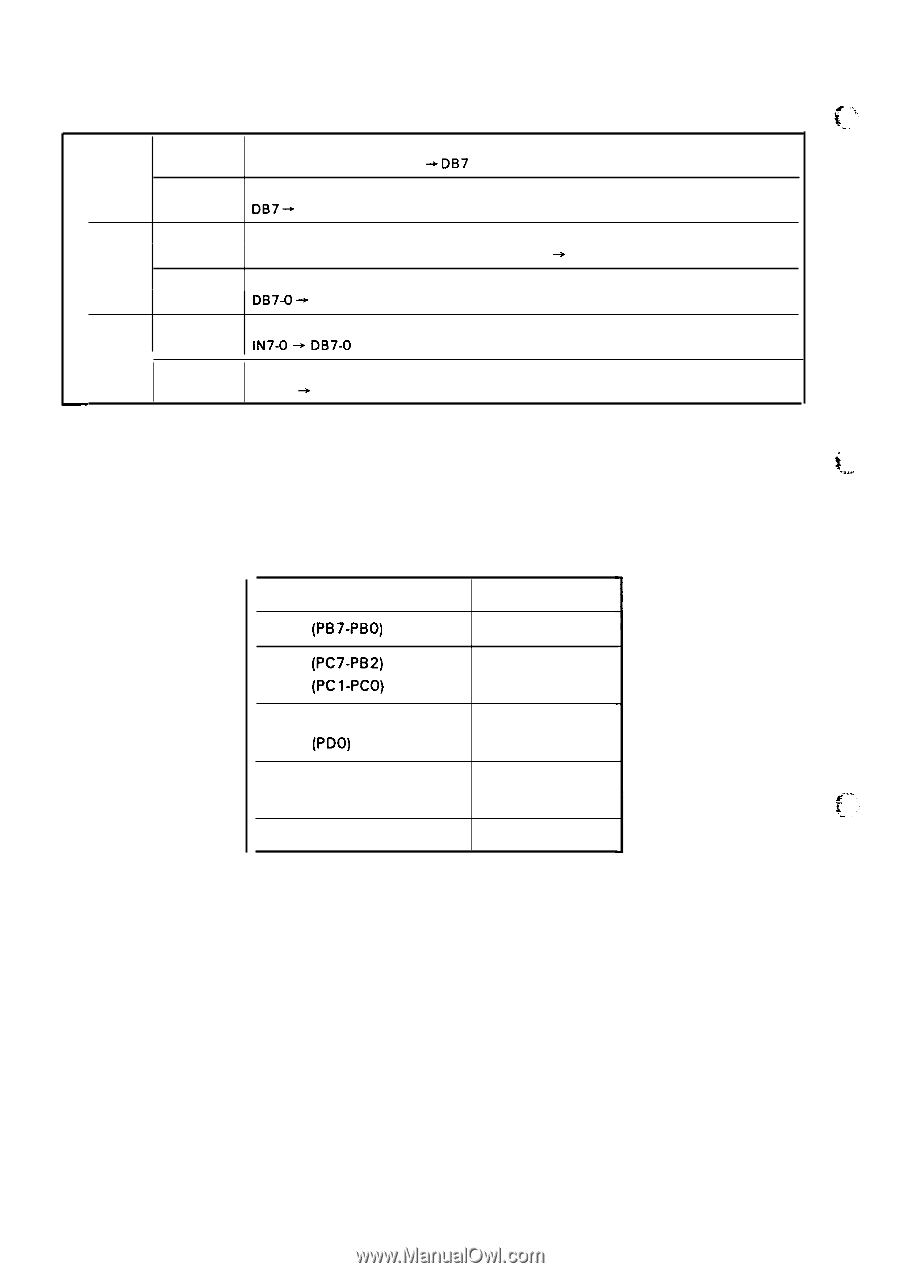

Table A-1 O. GA E05A16GA Control Functions cent'd

|

View all Epson LQ 1050 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 204 highlights

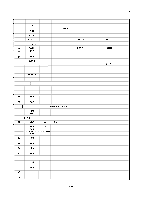

REV.-A 05H 06H 07H Table A-1 O. GA E05A16GA Control Functions (cent'd) READ WRITE READ WRITE READ WRITE Read the 9th pin data of the Super/Subscript generator. Interface parameter bit 7 ~ DB7 Write the 9th pin data to the Super/Subscript generator. DB7 ~ 9th pin data of the Super/Subscript generator. Read 8 bits data from the Super/Subscript generator. 8 bits data of the Super/Subscript generator ~ DB7-O. Write 8 bits data to the Super/Subscript generator. DB7-O ~ Super/Subscript generator. Read data from the parallel data latch. IN7-O ~ DB7-O Write data to the Super/Subscript generator and port D. DB 1-2 ~ PD 1-2 This gate array logically ANDs the two external reset signal inputs using internal logic, then outputs ~ the result to an external device (one-channel) and resets the ports internally. Table A-1 1 shows the port "" settings after they are reset. Table A-1 1. GA E05A16GA Initialized State Port Setting Port B (PB7-PBO) High port C (PC7-PB2) (PC1-PCO) Low High Port D (PD 1) (PDO) High Low Interface control port Low (except bit 2) (o) f-'. Hard-ware BUSY signal Low (Ready) A-18