Epson LQ 1050 Technical Manual - Page 203

REV.-A, MM1/O, DB7-O, IN7-O

|

View all Epson LQ 1050 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 203 highlights

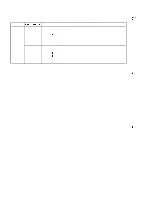

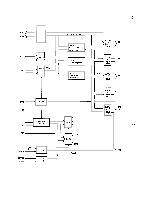

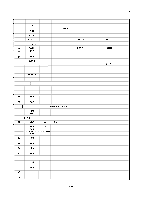

REV.-A This gate array is accessed by READing and WRITEing the memory mapped 1/0 addresses (MM IO) using the internal address decoder. The MMIO Ports for this gate array are OOH to 07H, accessed by the lower three bits (AO to A2) of the address bus. Table A-1 O shows the operation of the memory mapped 1/0 addresses. Table A-10. GA E05A16GA Control Functions MM1/O Address OOH 01 H 02H 03H 04H READ/ WRITE READ WRITE READ WRITE READ WRITE READ WRITE READ WRITE Control Functions PA7-O + DB7-O (Read) The data is inverted. DB7-O + PB7-O (Write) The data is inverted. IN7-O + DB7-O (Read) The data is inverted. DB7-O ~ PC7-O (Write) The data is inverted except bit O and 1. Read hard-ware BUSY signal (DBO) When DBO is high, parallel data is latched in gate array. Write interface parameter to interface control port. Bit 7: Print data O: "1" bit is print data; 1: "O" bit is print data. Bit 6: Acknowledge signal O: inactive state 1: active state Bit 5: Busy signal O: High level is active state. 1: Low level is active state. Bit 4: Software Busy signal O: Software Busy state. 1: Ready state. Bit 3: ERR signal O: inactive state. 1: active state. Bit 2: PE signal O: inactive state. 1: active state. Bit 1: Serial data input selection. O: IN7. 1 : RX DIN. Bit O: Parallel data latch timing. O: Rising edge of STRB. 1: Falling edge of STRB. Read the converted Italic CG data. The data is shifted at the falling edge of the RD signal. Shift out the MS bit of the 24 bits shift register. MSB24 ~ DB7 The data is shifted at the rising edge fo RD signal. Load shift register. 1st: DB7-O ~ Bit 23-16 2nd: DB7-O ~ Bit 15-8 3rd: DB7-O ~ Bit 7-O A-1 7