AMD AMD-K6-2/500AFX Data Sheet - Page 31

Instruction Fetch and Decode, Instruction Fetch

|

View all AMD AMD-K6-2/500AFX manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 31 highlights

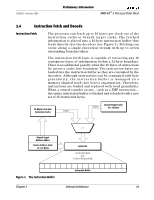

21850J/0-February 2000 Preliminary Information AMD-K6®-2 Processor Data Sheet 2.4 Instruction Fetch and Decode Instruction Fetch The processor can fetch up to 16 bytes per clock out of the instruction cache or branch target cache. The fetched information is placed into a 16-byte instruction buffer that feeds directly into the decoders (see Figure 3). Fetching can occur along a single execution stream with up to seven outstanding branches taken. The instruction fetch logic is capable of retrieving any 16 contiguous bytes of information within a 32-byte boundary. There is no additional penalty when the 16 bytes of instructions lie across a cache line boundary. The instruction bytes are loaded into the instruction buffer as they are consumed by the decoders. Although instructions can be consumed with byte granularity, the instruction buffer is managed on a memory-aligned word (two bytes) organization. Therefore, instructions are loaded and replaced with word granularity. When a control transfer occurs-such as a JMP instruction- the entire instruction buffer is flushed and reloaded with a new set of 16 instruction bytes. 32-Kbyte Level-One Instruction Cache 16 Bytes 16 Bytes Branch-Target Cache 16 x 16 Bytes Branch Target Address Adders Return Address Stack 16 x 16 Bytes 2:1 Fetch Unit 16 Instruction Bytes plus 16 Sets of Predecode Bits Figure 3. The Instruction Buffer Instruction Buffer Chapter 2 Internal Architecture 11