Intel S2600GZ S2600GZ/GL - Page 237

CATERR, P0 MSID Mismatch, CPU Missing, P1 MSID Mismatch, P1 VRD Hot, P2 VRD Hot

|

View all Intel S2600GZ manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 237 highlights

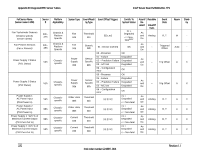

Appendix B: Integrated BMC Sensor Tables Intel® Server Board S2600GZ/GL TPS Full Sensor Name (Sensor name in SDR) Sensor # Processor 1 ERR2 Timeout 7Ch (P1 ERR2) Processor 2 ERR2 Timeout 7Dh (P2 ERR2) Catastrophic Error 80h (CATERR) Processor0 MSID Mismatch 81h (P0 MSID Mismatch) Processor Population Fault 82h (CPU Missing) Processor1 MSID Mismatch 87h (P1 MSID Mismatch) Processor 1 VRD Temperature 90h (P1 VRD Hot) Processor 2 VRD Temperature 91h (P2 VRD Hot) Processor 1 Memory VRD Hot 0-1 94h (P1 Mem01 VRD Hot) Processor 1 Memory VRD Hot 2-3 95h (P1 Mem23 VRD Hot) Platform Applicability All All All All All All All All All All Sensor Type Event/Readi Event Offset Triggers ng Type Processor 07h Processor 07h Processor 07h Processor 07h Processor 07h Processor 07h Temperature 01h Temperature 01h Temperature 01h Temperature 01h Digital Discrete 03h Digital Discrete 03h Digital Discrete 03h Digital Discrete 03h Digital Discrete 03h Digital Discrete 03h Digital Discrete 05h Digital Discrete 05h Digital Discrete 05h Digital Discrete 05h 01 - State Asserted 01 - State Asserted 01 - State Asserted 01 - State Asserted 01 - State Asserted 01 - State Asserted 01 - Limit exceeded 01 - Limit exceeded 01 - Limit exceeded 01 - Limit exceeded Contrib. To System Status fatal fatal fatal fatal Fatal fatal Non-fatal Non-fatal Non-fatal Non-fatal Assert/ De- assert As and De Readable Value/Of fsets - As and - De As and - De As and - De As and - De As and - De As and - De As and - De As and - De As and - De Event Data Trig Offset Trig Offset Trig Offset Trig Offset Trig Offset Trig Offset Trig Offset Trig Offset Trig Offset Trig Offset Rearm A A M M M M M M A A Standby 224 Revision 1.1 Intel order number G24881-004