Intel S2600GZ S2600GZ/GL - Page 245

Table 58. POST Progress Code LED Example, Table 59. POST Progress Codes

|

View all Intel S2600GZ manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 245 highlights

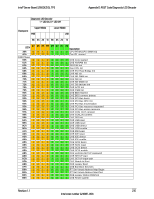

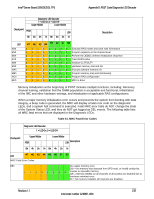

Appendix D: POST Code Diagnostic LED Decoder Intel® Server Board S2600GZ/GL TPS Table 58. POST Progress Code LED Example LEDs MSB LED #7 Upper Nibble AMBER LEDs LED #6 LED #5 LED #4 LED #3 Lower Nibble GREEN LEDs LED #2 LED #1 LSB LED #0 8h 4h 2h 1h 8h 4h 2h 1h Status ON OFF ON OFF ON ON OFF OFF Results 1 0 1 Ah 0 1 1 0 Ch 0 Upper nibble bits = 1010b = Ah; Lower nibble bits = 1100b = Ch; the two are concatenated as ACh The following table provides a list of all POST progress codes. Table 59. POST Progress Codes Diagnostic LED Decoder 1 = LED On, 0 = LED Off Checkpoint Upper Nibble MSB Lower Nibble LSB 8h 4h 2h 1h 8h 4h 2h 1h LED # #7 #6 #5 #4 #3 #2 #1 #0 Description SEC Phase 01h 0 0 0 0 0 0 0 1 First POST code after CPU reset 02h 0 0 0 0 0 0 1 0 Microcode load begin 03h 0 0 0 0 0 0 1 1 CRAM initialization begin 04h 0 0 0 0 0 1 0 0 Pei Cache When Disabled 05h 0 0 0 0 0 1 0 1 SEC Core At Power On Begin. 06h 0 0 0 0 0 1 1 0 Early CPU initialization during Sec Phase. 07h 0 0 0 0 0 1 1 1 Early SB initialization during Sec Phase. 08h 0 0 0 0 1 0 0 0 Early NB initialization during Sec Phase. 09h 0 0 0 0 1 0 0 1 End Of Sec Phase. 0Eh 0 0 0 0 1 1 1 0 Microcode Not Found. 0Fh 0 0 0 0 1 1 1 1 Microcode Not Loaded. PEI Phase 10h 0 0 0 1 0 0 0 0 PEI Core 11h 0 0 0 1 0 0 0 1 CPU PEIM 15h 0 0 0 1 0 1 0 1 NB PEIM 19h 0 0 0 1 1 0 0 1 SB PEIM MRC Process Codes - MRC Progress Code Sequence is executed - See Table 63 PEI Phase continued... 31h 0 0 1 1 0 0 0 1 Memory Installed 32h 0 0 1 1 0 0 1 0 CPU PEIM (Cpu Init) 33h 0 0 1 1 0 0 1 1 CPU PEIM (Cache Init) 34h 0 0 1 1 0 1 0 0 CPU PEIM (BSP Select) 35h 0 0 1 1 0 1 0 1 CPU PEIM (AP Init) 232 Revision 1.1 Intel order number G24881-004