Intel S2600CP Technical Product Specification - Page 165

All outputs must rise monotonically

|

View all Intel S2600CP manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 165 highlights

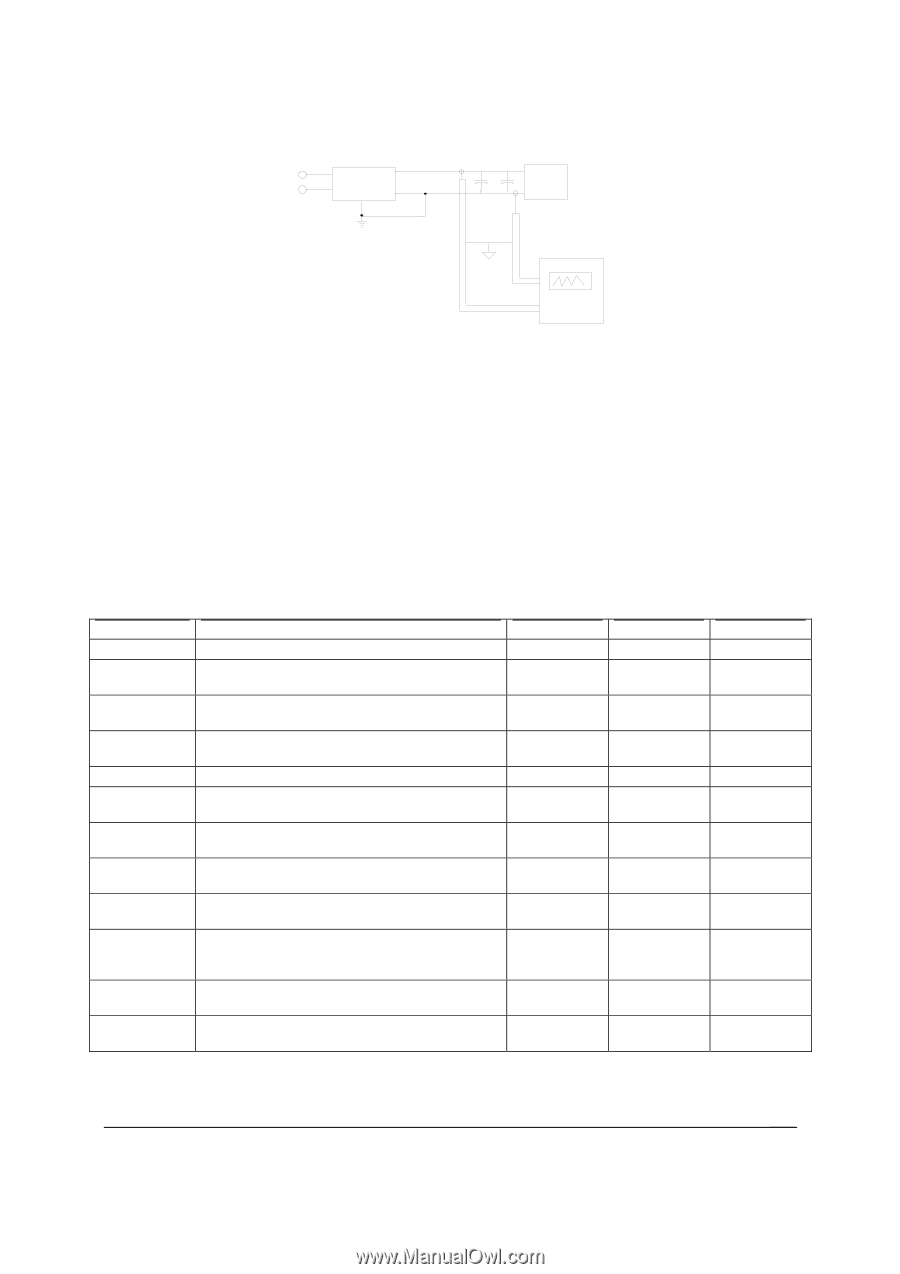

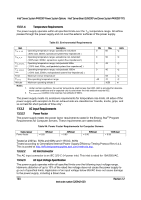

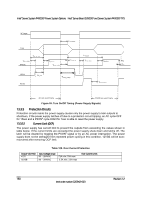

Intel® Server Board S2600CP and Server System P4000CP TPS Intel® Server System P4000CP Power System Options VOUT AC HOT POWER SUPPLY AC NEUTRAL VRETURN 10uF .1uF LOAD LOAD MUST BE ISOLATED FROM THE GROUND OF THE POWER SUPPLY AC GROUND GENERAL NOTES: 1. LOAD THE OUTPUT WITH ITS MINIMUM LOAD CURRENT. 2. CONNECT THE PROBES AS SHOWN. 3. REPEAT THE MEASUREMENTS WITH THE MAXIMUM LOAD ON THE OUTPUT. SCOPE SCOPE NOTE: USE A TEKTRONIX 7834 OSCILLOSCOPE WITH 7A13 AND DIFFERENTIAL PROBE P6055 OR EQUIVALENT. Figure 58. Differential Noise test setup Note: When performing this test, the probe clips and capacitors should be located close to the load. 13.3.4.12 Timing Requirements These are the timing requirements for the power supply operation. The output voltages must rise from 10% to within regulation limits (Tvout_rise) within 5 to 70ms. For 12VSB, it is allowed to rise from 1.0 to 25ms. All outputs must rise monotonically. Table below shows the timing requirements for the power supply being turned on and off by the AC input, with PSON held low and the PSON signal, with the AC input applied. Table 105. Timing Requirements Item Tvout_rise Tsb_on_delay Tac_on_delay Tvout_holdup Tpwok_holdup Tpson_on_delay Tpson_pwok Tpwok_on T pwok_off Tpwok_low Tsb_vout T12VSB_holdup Description Output voltage rise time Delay from AC being applied to 12VSBbeing within regulation. Delay from AC being applied to all output voltages being within regulation. Time 12Vl output voltage stay within regulation after loss of AC. Delay from loss of AC to de-assertion of PWOK Delay from PSON# active to output voltages within regulation limits. Delay from PSON# deactivate to PWOK being deasserted. Delay from output voltages within regulation limits to PWOK asserted at turn on. Delay from PWOK de-asserted to output voltages dropping out of regulation limits. Duration of PWOK being in the de-asserted state during an off/on cycle using AC or the PSON signal. Delay from 12VSBbeing in regulation to O/Ps being in regulation at AC turn on. Time the 12VSBoutput voltage stays within regulation after loss of AC. Min 5.0 * 13 12 5 100 1 100 50 70 Max 70 * 1500 3000 400 5 500 1000 Units ms ms ms ms ms ms ms ms ms ms ms ms * The 12VSBoutput voltage rise time shall be from 1.0ms to 25ms. Revision 1.2 149 Intel order number G26942-003