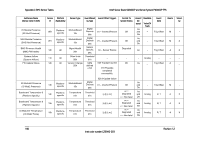

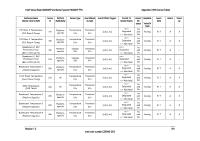

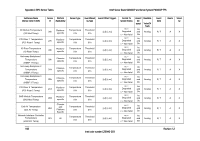

Intel S2600CP Technical Product Specification - Page 201

P1 Therm Ctrl, P2 Therm Ctrl, P3 Therm Ctrl, P4 Therm Ctrl

|

View all Intel S2600CP manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 201 highlights

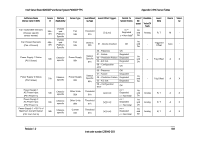

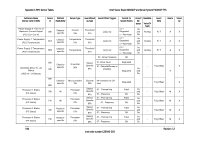

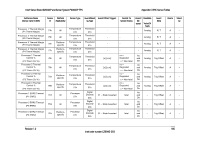

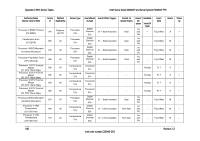

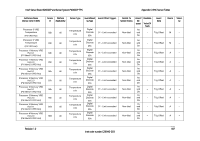

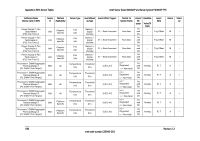

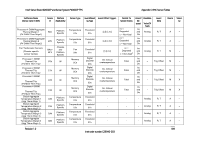

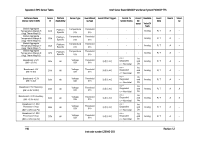

Intel® Server Board S2600CP and Server System P4000CP TPS Appendix C: BMC Sensor Tables Full Sensor Name (Sensor name in SDR) Sensor Platform # Applicability Processor 1 Thermal Margin (P1 Therm Margin) 74h All Processor 2 Thermal Margin (P2 Therm Margin) 75h All Processor 3 Thermal Margin (P3 Therm Margin) 76h Platformspecific Processor 4 Thermal Margin (P4 Therm Margin) 77h Platformspecific Processor 1 Thermal Control % (P1 Therm Ctrl %) Processor 2 Thermal Control % (P2 Therm Ctrl %) Processor 3 Thermal Control % (P3 Therm Ctrl %) Processor 4 Thermal Control % (P4 Therm Ctrl %) 78h All 79h All 7Ah Platformspecific 7Bh Platformspecific Processor 1 ERR2 Timeout 7Ch All (P1 ERR2) Processor 2 ERR2 Timeout (P2 ERR2) 7Dh All Processor 3 ERR2 Timeout (P3 ERR2) 7Eh Platformspecific Sensor Type Temperature 01h Temperature 01h Temperature 01h Temperature 01h Temperature 01h Temperature 01h Temperature 01h Temperature 01h Processor 07h Processor 07h Processor 07h Event/Readi ng Type Threshold 01h Threshold 01h Threshold 01h Threshold 01h Threshold 01h Threshold 01h Threshold 01h Threshold 01h Digital Discrete 03h Digital Discrete 03h Digital Discrete 03h Event Offset Triggers [u] [c,nc] [u] [c,nc] [u] [c,nc] [u] [c,nc] 01 - State Asserted 01 - State Asserted 01 - State Asserted Contrib. To System Status Assert/ De- assert Readable Value/Of fsets - - Analog Event Data R, T - - Analog R, T - - Analog R, T - - Analog R, T nc = Degraded c = Non-fatal As and Analog Trig Offset De nc = Degraded c = Non-fatal As and Analog Trig Offset De nc = Degraded c = Non-fatal As and Analog Trig Offset De nc = Degraded c = Non-fatal As and Analog Trig Offset De As fatal and - Trig Offset De As fatal and - Trig Offset De As fatal and - Trig Offset De Rearm A A A A A A A A A A A Standby Revision 1.2 185 Intel order number G26942-003