Intel S2600CP Technical Product Specification - Page 80

Diagnostic Interrupt NMI Button, BMC Watchdog

|

View all Intel S2600CP manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 80 highlights

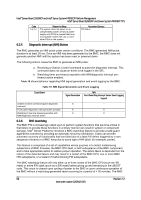

Intel® Server Board S2600CP and Intel® Server System P4000CP Platform Management Intel® Server Board S2600CP and Server System P4000CP TPS 6.2.5 Code 1-5-1-4 Reason for Beep The system does not power on or unexpectedly powers off and a power supply unit (PSU) is present that is an incompatible model with one or more other PSUs in the system Diagnostic Interrupt (NMI) Button Associated Sensors PS Status The BMC generates an NMI pulse under certain conditions. The BMC-generated NMI pulse duration is at least 30 ms. Once an NMI has been generated by the BMC, the BMC does not generate another NMI until the system has been reset or powered down. The following actions cause the BMC to generate an NMI pulse: a. Receiving a Chassis Control command to pulse the diagnostic interrupt. This command does not cause an event to be logged in the SEL. b. Watchdog timer pre-timeout expiration with NMI/diagnostic interrupt pretimeout action enabled. Table 16 shows behavior regarding NMI signal generation and event logging by the BMC. Table 16. NMI Signal Generation and Event Logging Causal Event Signal Generation NMI Front Panel Diag Interrupt Sensor Event Logging Support Chassis Control command (pulse diagnostic X - interrupt) Front panel diagnostic interrupt button pressed X X Watchdog Timer pre-timeout expiration with X X NMI/diagnostic interrupt action 6.2.6 BMC Watchdog The BMC FW is increasingly called upon to perform system functions that are time-critical in that failure to provide these functions in a timely manner can result in system or component damage. Intel® Server Platforms introduce a BMC watchdog feature to provide a safe-guard against this scenario by providing an automatic recovery mechanism. It also can provide automatic recovery of functionality that has failed due to a fatal FW defect triggered by a rare sequence of events or a BMC hang due to some type of HW glitch (for example, power). This feature is comprised of a set of capabilities whose purpose is to detect misbehaving subsections of BMC firmware, the BMC CPU itself, or HW subsystems of the BMC component, and to take appropriate action to restore proper operation. The action taken is dependent on the nature of the detected failure and may result in a restart of the BMC CPU, one or more BMC HW subsystems, or a restart of malfunctioning FW subsystems. The BMC watchdog feature will only allow up to three resets of the BMC CPU (such as HW reset) or entire FW stack (such as a SW reset) before giving up and remaining in the uBOOT code. This count is cleared upon cycling of power to the BMC or upon continuous operation of the BMC without a watchdog-generated reset occurring for a period of > 30 minutes. The BMC 64 Revision 1.2 Intel order number G26942-003