Intel S2600CP Technical Product Specification - Page 78

Server Management Functional Specifications

|

View all Intel S2600CP manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 78 highlights

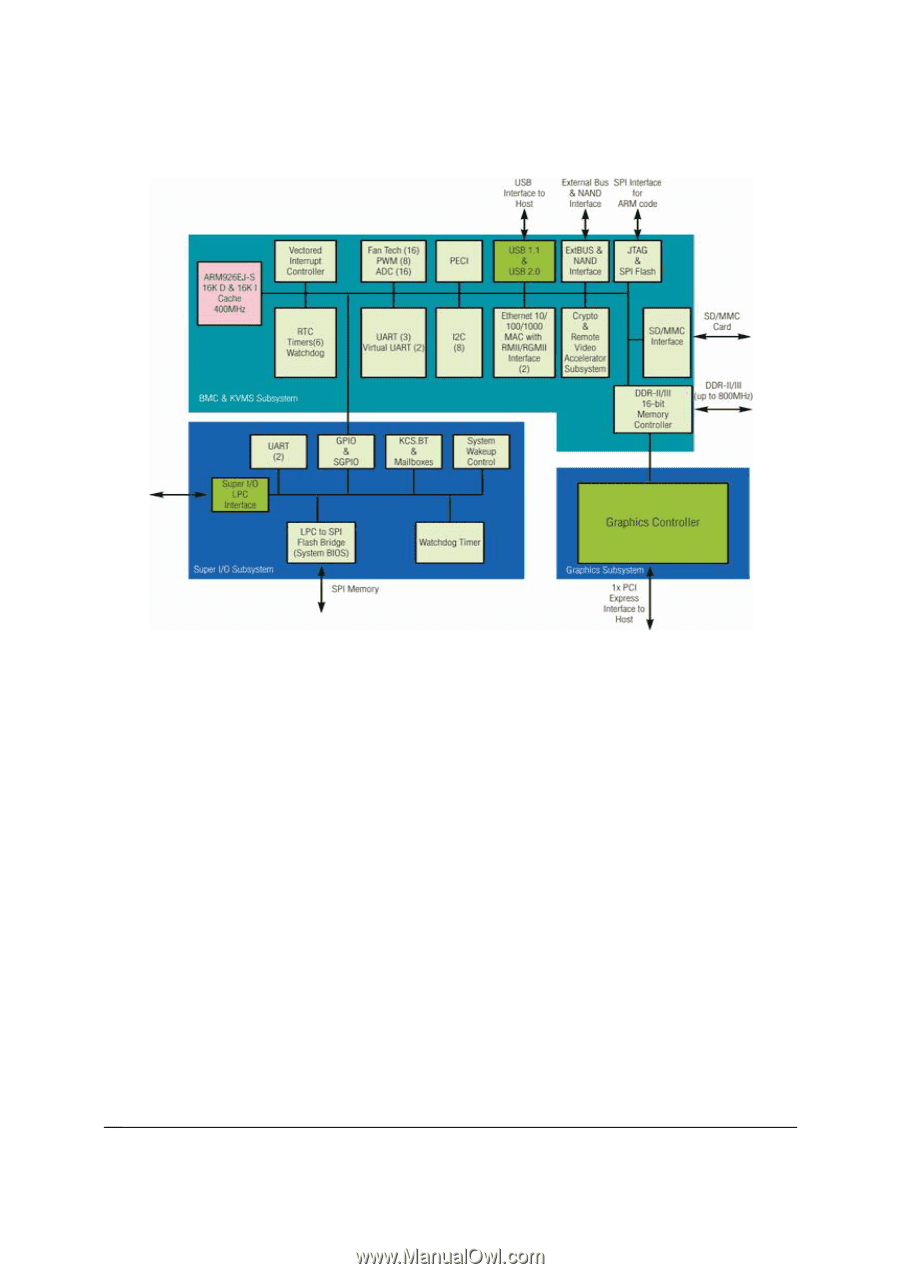

Intel® Server Board S2600CP and Intel® Server System P4000CP Platform Management Intel® Server Board S2600CP and Server System P4000CP TPS Figure 28. Integrated BMC Hardware 6.2 Server Management Functional Specifications 6.2.1 BMC Internal Timestamp Clock The BMC maintains an internal timestamp clock that is used by various BMC subsystems, for example, for time stamping SEL entries. As part of BMC initialization after AC power is applied or the BMC is reset, the BMC initializes this internal clock to the value retrieved from the SSB component's RTC by a SMBus* slave read operation. This is the system RTC and is on the battery power well so it maintains the current time even when there is no AC supplied to the system. 6.2.1.1 System Clock Synchronization The BIOS must send the Set SEL Time command with the current system time to the BMC during system Power-on Self-Test (POST). Synchronization during very early POST is preferred, so that any SEL entries recorded during system boot can be accurately time stamped. Additionally, during sleep state transitions other than S0 the BIOS will synchronize the time. If the time is modified through an OS interface, then the BMC's time is not synchronized until the next system reboot. 62 Revision 1.2 Intel order number G26942-003