Intel S2600CP Technical Product Specification - Page 48

Integrated Memory Controller IMC and Memory Subsystem

|

View all Intel S2600CP manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 48 highlights

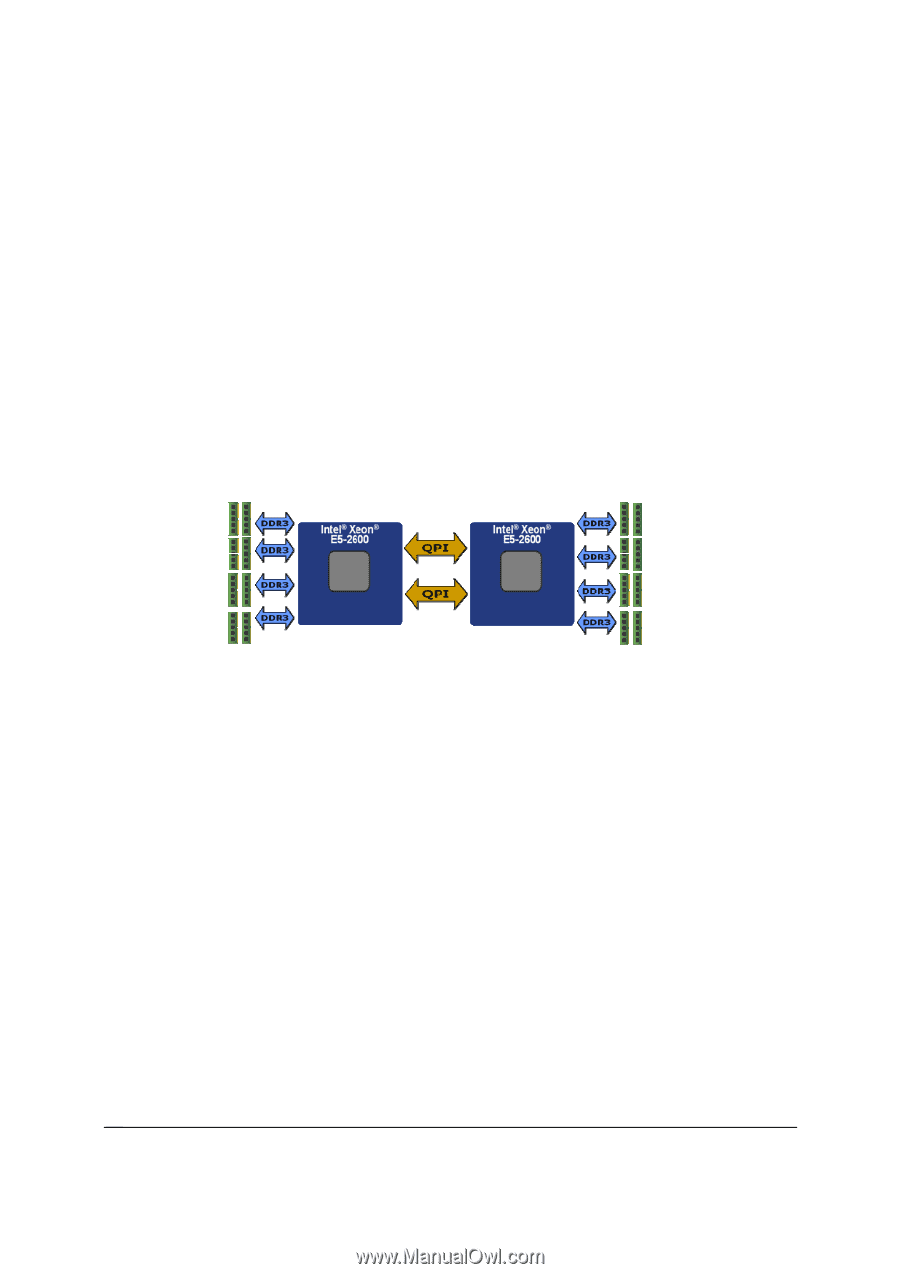

Intel® Server Board S2600CP Functional Architecture Intel® Server Board S2600CP and Server System P4000CP TPS interconnect performance to be achieved in real systems. It has a snoop protocol optimized for low latency and high scalability, as well as packet and lane structures enabling quick completions of transactions. Reliability, availability, and serviceability features (RAS) are built into the architecture. The physical connectivity of each interconnect link is made up of twenty differential signal pairs plus a differential forwarded clock. Each port supports a link pair consisting of two uni-directional links to complete the connection between two components. This supports traffic in both directions simultaneously. To facilitate flexibility and longevity, the interconnect is defined as having five layers: Physical, Link, Routing, Transport, and Protocol. The Intel® QuickPath Interconnect includes a cache coherency protocol to keep the distributed memory and caching structures coherent during system operation. It supports both low-latency source snooping and a scalable home snoop behavior. The coherency protocol provides for direct cache-to-cache transfers for optimal latency. 4.2.2 Integrated Memory Controller (IMC) and Memory Subsystem CPU 1 CPU 2 2 DIMMs/Ch 2 DIMMs/Ch Figure 21. Memory Subsystem for Intel® Server Board S2600CP Integrated into the processor is a memory controller. Each processor provides four DDR3 channels that support the following: Unbuffered DDR3 and registered DDR3 DIMMs LR DIMM (Load Reduced DIMM) for buffered memory solutions demanding higher capacity memory subsystems Independent channel mode or lockstep mode Data burst length of eight cycles for all memory organization modes Memory DDR3 data transfer rates of 800, 1066, 1333, and 1600 MT/s 64-bit wide channels plus 8-bits of ECC support for each channel DDR3 standard I/O Voltage of 1.5 V and DDR3 Low Voltage of 1.35 V 1-Gb, 2-Gb, and 4-Gb DDR3 DRAM technologies supported for these devices: o UDIMM DDR3 - SR x8 and x16 data widths, DR - x8 data width o RDIMM DDR3 - SR,DR, and QR - x4 and x8 data widths o LRDIMM DDR3 - QR - x4 and x8 data widths with direct map or with rank multiplication Up to 8 ranks supported per memory channel, 1, 2 or 4 ranks per DIMM Open with adaptive idle page close timer or closed page policy 32 Revision 1.2 Intel order number G26942-003