Intel S2600CP Technical Product Specification - Page 53

Independent Channel Mode, 2.2.4.2, Rank Sparing Mode, 2.2.4.3, Mirrored Channel Mode, 2.2.4

|

View all Intel S2600CP manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 53 highlights

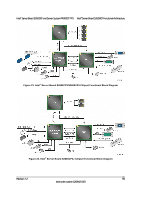

Intel® Server Board S2600CP and Server System P4000CP TPS Intel® Server Board S2600CP Functional Architecture Independent Channel Mode Rank Sparing Mode Mirrored Channel Mode Lockstep Channel Mode Regardless of RAS mode, the requirements for populating within a channel given in the section 4.2.2.2 must be met at all times. Note that support of RAS modes that require matching DIMM population between channels (Mirrored and Lockstep) require that ECC DIMMs be populated. Independent Channel Mode is the only mode that supports non-ECC DIMMs in addition to ECC DIMMs. For RAS modes that require matching populations, the same slot positions across channels must hold the same DIMM type with regards to size and organization. DIMM timings do not have to match but timings will be set to support all DIMMs populated (i.e, DIMMs with slower timings will force faster DIMMs to the slower common timing modes). 4.2.2.4.1 Independent Channel Mode Channels can be populated in any order in Independent Channel Mode. All four channels may be populated in any order and have no matching requirements. All channels must run at the same interface frequency but individual channels may run at different DIMM timings (RAS latency, CAS Latency, and so forth). 4.2.2.4.2 Rank Sparing Mode In Rank Sparing Mode, one rank is a spare of the other ranks on the same channel. The spare rank is held in reserve and is not available as system memory. The spare rank must have identical or larger memory capacity than all the other ranks (sparing source ranks) on the same channel. After sparing, the sparing source rank will be lost. 4.2.2.4.3 Mirrored Channel Mode In Mirrored Channel Mode, the memory contents are mirrored between Channel 0 and Channel 2 and also between Channel 1 and Channel 3. As a result of the mirroring, the total physical memory available to the system is half of what is populated. Mirrored Channel Mode requires that Channel 0 and Channel 2, and Channel 1 and Channel 3 must be populated identically with regards to size and organization. DIMM slot populations within a channel do not have to be identical but the same DIMM slot location across Channel 0 and Channel 2 and across Channel 1 and Channel 3 must be populated the same. 4.2.2.4.4 Lockstep Channel Mode In Lockstep Channel Mode, each memory access is a 128-bit data access that spans Channel 0 and Channel 1, and Channel 2 and Channel 3. Lockstep Channel mode is the only RAS mode that allows SDDC for x8 devices. Lockstep Channel Mode requires that Channel 0 and Channel 1, and Channel 2 and Channel 3 must be populated identically with regards to size and organization. DIMM slot populations within a channel do not have to be identical but the same DIMM slot location across Channel 0 and Channel 1 and across Channel 2 and Channel 3 must be populated the same. Revision 1.2 37 Intel order number G26942-003