Intel SE7525GP2 Product Specification - Page 126

Power-up Sequence, 3.1.2, Power-down Sequence, 3.1.3, Power Control Sources

|

View all Intel SE7525GP2 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 126 highlights

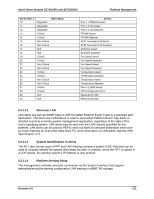

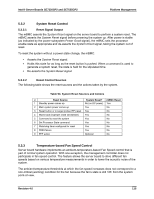

Platform Management Intel® Server Boards SE7320SP2 and SE7525GP2 5.3.1.1 Power-up Sequence When turning on the system power in response to one of the event occurrences listed in Table 53 below, the mBMC executes the following procedure: ƒ The mBMC asserts Power On and waits for the power subsystem to assert Power Good. The system is held in reset. ƒ The mBMC sends a Set ACPI Power State command, indicating an S0 state to all management controllers whose SDR management device records indicate that they should receive the notification. ƒ The mBMC initializes all sensors to their Power On initialization state. The Init Agent is run. ƒ The mBMC attempts to boot the system by running the FRB algorithm. 5.3.1.2 Power-down Sequence To power down the system, the mBMC effectively performs the sequence of power-up steps in reverse order. This operation can be initiated by one of the event occurrences listed in Table 53 and proceeds as follows: ƒ The mBMC asserts system reset (de-asserts Power Good). ƒ If enabled, the mBMC sends a Set ACPI Power State command, indicating an S0 state to all management controllers whose SDR management device records indicate that they should receive the notification. ƒ The mBMC de-asserts the Power On signal. ƒ The power subsystem turns off system power upon de-assertion of the Power On signal. 5.3.1.3 Power Control Sources The sources listed in the following table can initiate power-up and/or power-down activity. Table 53. Power Control Initiators # Source 1 Power Button External Signal Name or Internal Subsystem FP Power button Capabilities Turns power on or off 2 mBMC Watchdog Timer Internal mBMC timer Turns power off, or power cycle 3 Platform Event Filtering PEF Turns power off, or power cycle 4 Command Routed through command processor Turns power on or off, or power cycle 5 Power state retention Implemented via mBMC internal logic Turns power on when AC power returns 6 Chipset Sleep S5 Turns power on or off 114 Revision 4.0