Intel SE7525GP2 Product Specification - Page 53

Intel® Server Boards SE7320SP2 and SE7525GP2, Functional Architecture, Revision 4.0, Table 15. Super

|

View all Intel SE7525GP2 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 53 highlights

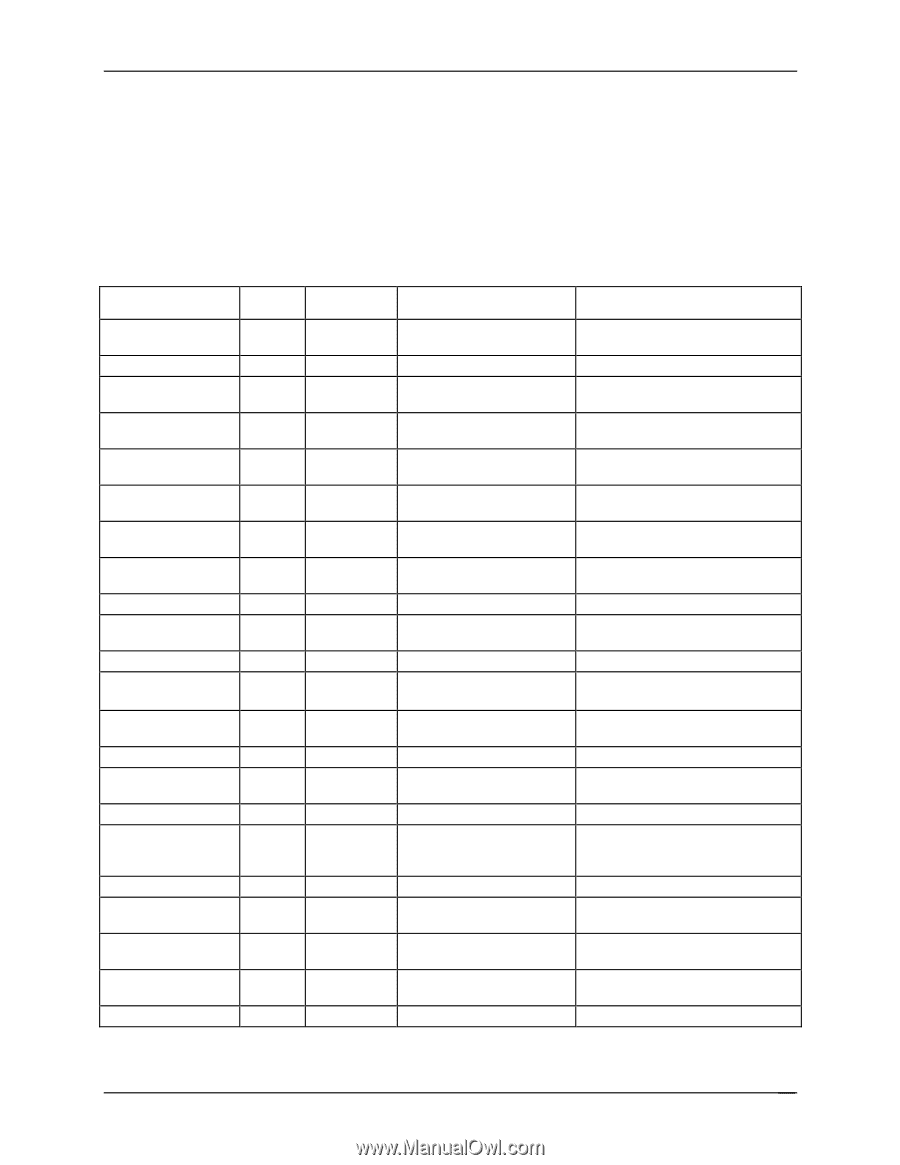

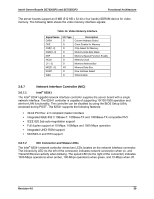

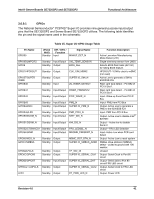

Intel® Server Boards SE7320SP2 and SE7525GP2 Functional Architecture 3.6.9.1 GPIOs The National Semiconductor* PC87427 Super I/O provides nine general-purpose input/output pins that the SE7320SP2 and Server Board SE7525GP2 utilizes. The following table identifies the pin and the signal name used in the schematic: Table 15. Super I/O GPIO Usage Table Pin Name GPIO00 (Powe Well) Standby GPIO05/LMPCIF2 GPIO6 GPIO7/HFCKOUT Standby Standby Standby GPIO27/SUPER IOSMI GPIOE40 GPIOE41 Standby Standby Standby GPIOE42 GPIOE43 GPIOE44/SCI Standby Standby Standby GPIOE45/LED GPIO50/DCDM_N Standby Standby GPIO51/DSRM_N Standby GPIO52/CTSM/XCS1 Standby GPIO54/SINM Standby GPO60/WDO_N GPO61/SMBSA Standby Standby GPO62/LFCLK GPEXC/GPIO56 Standby Standby GPEXD/GPIO57 Standby GPEXC2 / LMPCLK Standby LED1 Standby GPI / GPO / Function Input Input/Output Output Output Output Input Input/Output Input/Output Input/Output Input/Output Input/Output Input/Output Input/Output Input/Output Input/Output Output Output Output Output Input/Output Output Output Signal Name MANUF_DET_N SIO_TEMP_SENSOR BIOS_SEL CLK_10M_MBMC SUPER IO_SMI_N 2U_RISER_DETECT RISER_PRESENT2 PCIE_WAKE_N PME_N SUPER IO_PME_N PME_PCIX_N NWY_DIS_N KNI_DIS_N FRU_LEDSEL_N MROMB_PRESENT_N MBMC_RST_BTN_N SUPER IO_SMBUS_ADDR TP_SIO_45 SUPER IO_SERIAL_CLK1 SUPER IO_SERIAL_DAT SUPER IO_SERIAL_CLK2 FP_PWR_LED_N Function Description Active Low when Manufacturing Mode Detect (J35) Single wire temp sensor from LM30. Selects BIOS flash bank (A21 bit) for rolling BIOS feature. HFCKOUT- 10 MHz clock to mBMC (not used) Active Low to generate a SMI to 6300ESB ICH Riser card type detect - Pin B92 of PCI-X Slot 1. Riser card type detect - Pin B93 of PCI-X Slot 1. Input- Wake up Event from PCI-E Bus Intput- PME from PCI Bus Output- Active Low to generate a PME to the 6300ESB ICH Input- PME from PCI-X Bus Output- Active Low to disable Intel® 82570EI Output - Active low to disable Kenai-II Output - FRU LED Selection Input- Active Low when ZCR card detect Output- Active Low to reset system SMBus slave address (SMBSA) select - pulled to ground with 10K resistor. Unused Output- Serial Clock to Port 80 circuit Output- Serial data to Port 80 circuit/FRU LED circuit Output- Serial Clock to FRU LED circuit Output- Power LED Revision 4.0 41