Intel SE7525GP2 Product Specification - Page 62

I/O Map

|

View all Intel SE7525GP2 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 62 highlights

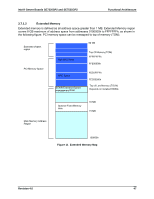

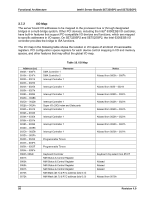

Functional Architecture Intel® Server Boards SE7320SP2 and SE7525GP2 3.7.2 I/O Map The server board I/O addresses to be mapped to the processor bus or through designated bridges in a multi-bridge system. Other PCI devices, including the Intel® 6300ESB I/O controller, have built-in features that support PC-compatible I/O devices and functions, which are mapped to specific addresses in I/O space. On SE7320SP2 and SE7525GP2, the Intel 6300ESB I/O controller provides the bridge to ISA functions. The I/O map in the following table shows the location in I/O space of all direct I/O-accessible registers. PCI configuration space registers for each device control mapping in I/O and memory spaces, and other features that may affect the global I/O map. Address (es) 0000h - 000Fh 0010h - 001Fh 0020h - 0021h 0022h - 0023h 0024h - 0025h 0026h - 0027h 0028h - 0029h 002Ah - 002Bh 002Ch - 002Dh 002Eh - 002Fh 0030h - 0031h 0032h - 0033h 0034h - 0035h 0036h - 0037h 0038h - 0039h 003Ah - 003Bh 003Ch - 003Dh 003Eh - 003Fh 0040h - 0043h 0044h - 004Fh 0050h - 0053F 0054h - 005Fh 0060h, 0064h 0061h 0063h 0065h 0067h 0070h 0072h Table 18. I/O Map Resource DMA Controller 1 DMA Controller 2 Interrupt Controller 1 Interrupt Controller 1 Interrupt Controller 1 Interrupt Controller 1 Super I/O (SIO) index and Data ports Interrupt Controller 1 Interrupt Controller 1 Interrupt Controller 1 Interrupt Controller 1 Programmable Timers Programmable Timers Keyboard Controller NMI Status & Control Register NMI Status & Control Register NMI Status & Control Register NMI Status & Control Register NMI Mask (bit 7) & RTC address (bits 6::0) NMI Mask (bit 7) & RTC address (bits 6::0) Notes Aliased from 0000h - 000Fh Aliased from 0020 - 0021h Aliased from 0020h - 0021h Aliased from 0020h - 0021h Aliased from 0020h - 0021h Aliased from 0020h - 0021h Aliased from 0020h - 0021h Aliased from 0020h - 0021h Keyboard chip select from 87417 Aliased Aliased Aliased Aliased from 0070h 50 Revision 4.0