Intel SE7525GP2 Product Specification - Page 44

Split Option ROM, Interrupt Routing

|

View all Intel SE7525GP2 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 44 highlights

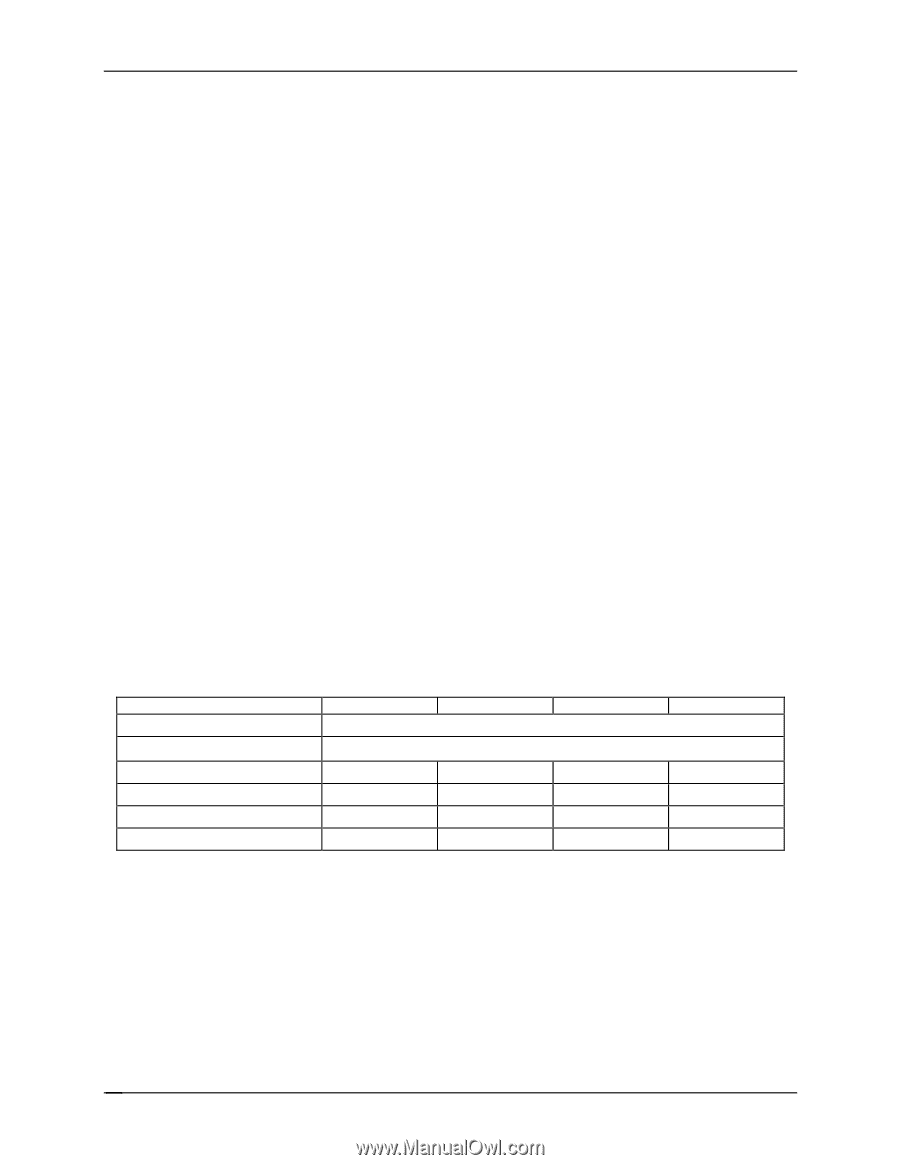

Functional Architecture Intel® Server Boards SE7320SP2 and SE7525GP2 3.6.1.9 PCI APIs The system BIOS supports the INT 1Ah, AH = B1h functions as defined in the PCI BIOS Specification. The system BIOS supports the real mode interfaces and does not support the protected mode interfaces. 3.6.2 Split Option ROM The BIOS supports the split option ROM algorithm per the PCI 3.0 specification. 3.6.3 Interrupt Routing The interrupt architecture accommodates both PC-compatible PIC mode and APIC mode interrupts through use of the integrated I/O APICs in the Intel 6300ESB I/O controller. 3.6.3.1 Legacy Interrupt Routing For PC-compatible mode, the Intel 6300ESB I/O controller provides two 82C59-compatible interrupt controllers. The two controllers are cascaded with interrupt levels 8-15 entering on level 2 of the primary interrupt controller (standard PC configuration). A single interrupt signal is presented to the processors, to which only one processor will respond for servicing. The Intel 6300ESB I/O controller contains configuration registers that define which interrupt source logically maps to I/O APIC INTx pins. Interrupts, both PCI and IRQ types, are handled by the Intel 6300ESB I/O controller. The Intel 6300ESB I/O controller then translates these to the APIC bus. The numbers in the table below indicate the Intel 6300ESB I/O controller PCI interrupt input pin to which the associated device interrupt (INTA, INTB, INTC, INTD) is connected. The Intel 6300ESB I/O controller I/O APIC exists on the I/O APIC bus with the processors. Interrupt Video Intel® 82541 NIC PCI Slot 3 (PCI 32b/33M) PCI Slot 5 (PCI 32b/33M) PCI Slot 2 (64b/66M) PCI Slot 1 (64b/66M) Table 11. PCI Interrupt Routing/Sharing INT A PIRQB PIRQA PIRQF PIRQE PXIRQ1 PXIRQ0 INT B PIRQD PIRQB PXIRQ2 PXIRQ1 INT C PIRQB PIRQH PXIRQ3 INT D PIRQH PIRQD PXIRQ0 3.6.3.2 APIC Interrupt Routing For APIC mode, interrupt architecture incorporates three Intel I/O APIC devices to manage and broadcast interrupts to local APICs in each processor. The Intel I/O APICs monitor each interrupt on each PCI device including PCI slots in addition to the ISA compatibility interrupts IRQ(0-15). When an interrupt occurs, a message corresponding to the interrupt is sent across a three-wire serial interface to the local APICs. The APIC bus minimizes interrupt latency time for 32 Revision 4.0