Intel SE7525GP2 Product Specification - Page 60

Main Memory, PCI Memory Space, High BIOS, I/O APIC Configuration Space, Extended lntel, Processor

|

View all Intel SE7525GP2 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 60 highlights

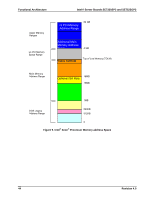

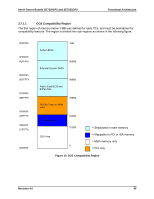

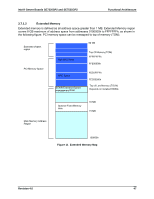

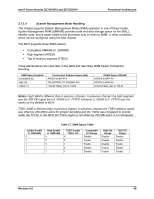

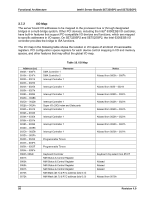

Functional Architecture Intel® Server Boards SE7320SP2 and SE7525GP2 ƒ Main Memory All installed memory greater than 1 MB is mapped to local main memory, up to 8 GB of physical memory. Memory between 1 MB to 15 MB is considered to be standard ISA extended memory. 1 MB of memory starting at 15 MB can be optionally mapped to the PCI bus memory space. The remainder of this space, up to 8 GB, is always mapped to main memory, unless TBSG SMM is used which just under TOLM. The range can be from 128 KB till 1 MB. 1 MB depends on the BIOS setting C SMRAM is used which limits the top of memory to 256 MB. BIOS occupies 512 KB for 32-bit SMI handler. ƒ PCI Memory Space Memory addresses below 4 GB range are mapped to the PCI bus. This region is divided into three sections: High BIOS, APIC Configuration Space, and General-purpose PCI Memory. The General-purpose PCI Memory area is typically used memory-mapped I/O to PCI devices. The memory address space for each device is set using PCI configuration registers. ƒ High BIOS The top 1 MB of Extended Memory under 4 GB is reserved for the system BIOS, extended BIOS for PCI devices, and A20 aliasing by the system BIOS. The lntel® Xeon® processor begins executing from the high BIOS region after reset. ƒ I/O APIC Configuration Space A 64 KB block located 20 MB below 4 GB (0FEC00000 to 0FEC0FFFFh) is reserved for the I/O APIC configuration space. The first I/O APIC is located at FEC00000h. The second I/O APIC is located at FEC80000h. The third I/O APIC is located at FEC80100h. ƒ Extended lntel® Xeon® Processor Region (above 4 GB) An lntel® Xeon® processor based system can have up to 64 GB of addressable memory. With the chipset only supporting 16 GB of addressable memory, the BIOS uses an extended addressing mechanism to use the address ranges. 3.7.1.3 Memory Shadowing System BIOS and option ROM can be shadowed in main memory. Typically this is done to allow ROM code to execute more rapidly out of RAM. ROM is designated read-only during the copy process while RAM at the same address is designated write-only. After copying, the RAM is designated read-only. After the BIOS is shadowed, the attributes for that memory area are set to read only so that all writes are forwarded to the expansion bus. 48 Revision 4.0