Brother International HL 1850 Service Manual - Page 87

EEPROM, 1870N, M24C64, method, configuration., Reset, circuit, reset, S-80928ANMP., voltage, period

|

UPC - 012502603900

View all Brother International HL 1850 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 87 highlights

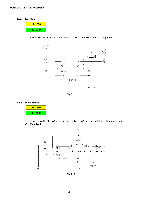

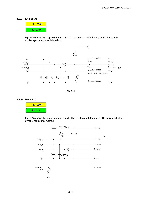

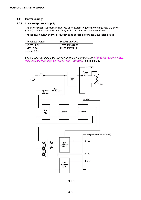

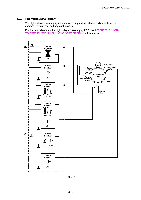

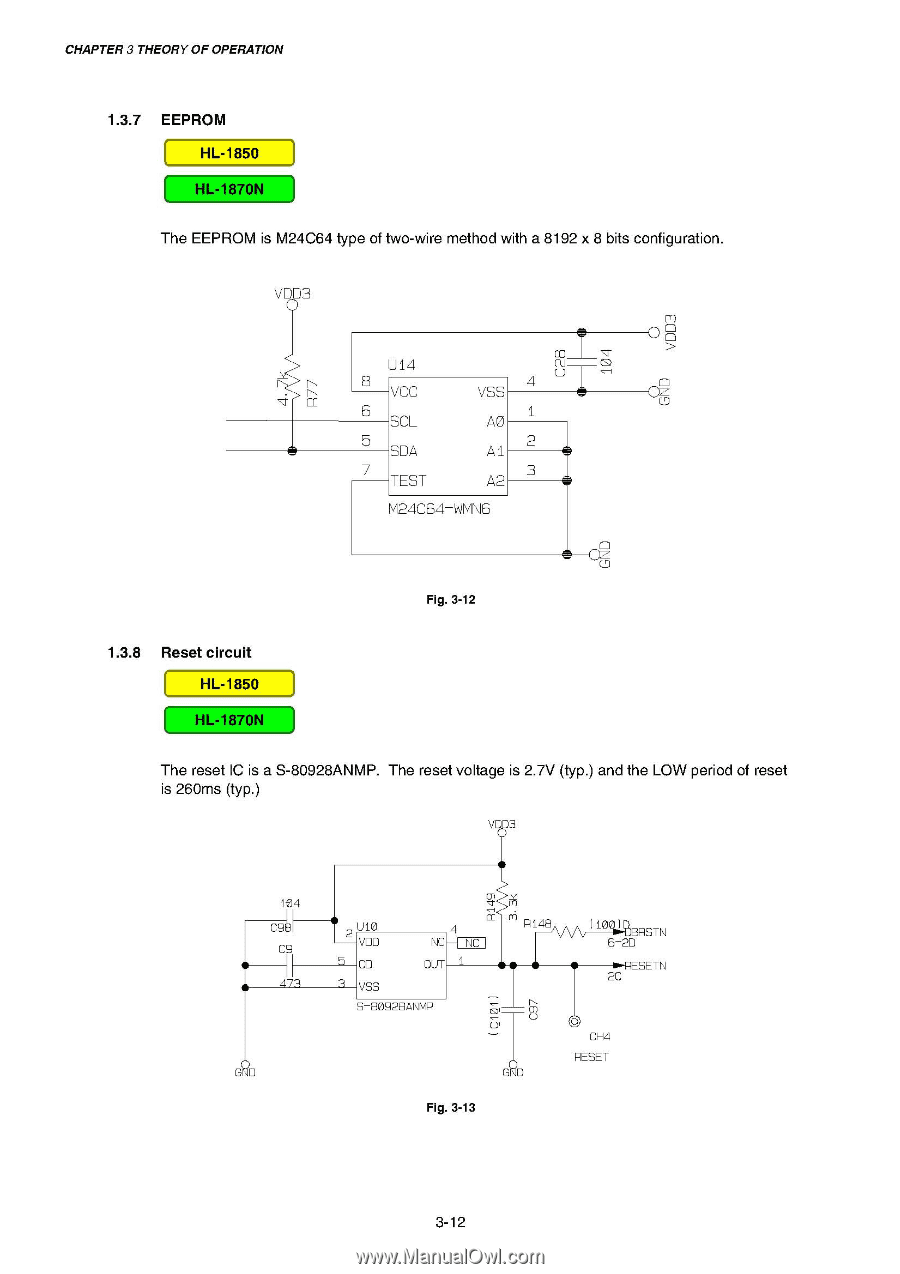

CHAPTER 3 THEORY OF OPERATION 1.3.7 EEPROM HL-1850 HL-1870N The EEPROM is M24C64 type of two-wire method with a 8192 x 8 bits configuration. VDD3 o U14 ccou >fs > Cc vcC 6 4 U vSS 0 Cz SCL AO 5 SDA Al 7 TEST A2 M24C64- WMN6 Fig. 3-12 1.3.8 Reset circuit HL-1850 HL-1870N The reset IC is a S-80928ANMP. The reset voltage is 2.7V (typ.) and the LOW period of reset is 260ms (typ.) VD83 104 (3_, C9 C9 473 2 U10 VDD 4 1ccrs-

CHAPTER

3

THEORY

OF

OPERATION

1.3.7

EEPROM

HL

-1850

HL

-1870N

The

EEPROM

is

M24C64

type

of

two

-wire

method

with

a

8192

x

8

bits

configuration.

VDD3

o

>

f

s

>

Cc

U14

6

5

7

vcC

vSS

SCL

AO

SDA

Al

TEST

A2

4

co

cu

U

M24C64

—

WMN6

Fig.

3-12

1.3.8

Reset

circuit

HL

-1850

HL

-1870N

0

Cz

The

reset

IC

is

a

S-80928ANMP.

The

reset

voltage

is

2.7V

(typ.)

and

the

LOW

period

of

reset

is

260ms

(typ.)

VD83

104

C9

(3_,

C9

U10

4

crs

1

-

<

>

In

•

c<

m

2

G

VDD

NCH

NC

5

-

CD

OUT

473

3

VSS

S

—

B0928ANMP

UI

Fig.

3-13

R

6

-

2D

low

RESETN

2C

CH4

RESET

3-12