AMD AMD-K6-2/400 User Guide - Page 305

Stop Clock State, Enter Stop Clock, State

|

View all AMD AMD-K6-2/400 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 305 highlights

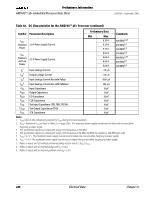

23542A/0-September 2000 Preliminary Information AMD-K6™-2E+ Embedded Processor Data Sheet 14.6 Stop Clock State Enter Stop Clock State If the CLK signal is stopped while the AMD-K6-2E+ processor is in the Stop Grant state, the processor enters the Stop Clock state. Because all internal clocks and the PLL are not running in the Stop Clock state, the Stop Clock state represents the minimum-power state of all clock control states. The CLK signal must be held Low while it is stopped. The Stop Clock state cannot be entered from the Halt state. INTR is the only input signal that is allowed to change states while the processor is in the Stop Clock state. However, INTR is not sampled until the processor returns to the Stop Grant state. All other input signals must remain unchanged in the Stop Clock state. Exit Stop Clock State The AMD-K6-2E+ processor returns to the Stop Grant state from the Stop Clock state after the CLK signal is started and the internal PLL has stabilized. PLL stabilization is achieved after the CLK signal has been running within its specification for a minimum of 1.0 ms. The frequency of CLK when exiting the Stop Clock state can be different than the frequency of CLK when entering the Stop Clock state. The state of the BF[2:0] signals when exiting the Stop Clock state is ignored because the BF[2:0] signals are only sampled during the falling transition of RESET. Chapter 14 Clock Control 283