AMD AMD-K6-2/400 User Guide - Page 311

Power Dissipation, AMD PowerNow! technology. - benchmarks

|

View all AMD AMD-K6-2/400 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 311 highlights

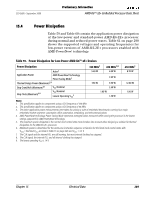

23542A/0-September 2000 Preliminary Information AMD-K6™-2E+ Embedded Processor Data Sheet 15.4 Power Dissipation Table 59 and Table 60 contain the application power dissipation of the low-power and standard-power AMD-K6-2E+ processor during normal and reduced power states. Table 61 on page 290 shows the supported voltages and operating frequencies for low-power versions of AMD-K6-2E+ processors enabled with AMD PowerNow! technology. Table 59. Power Dissipation for Low-Power AMD-K6™-2E+ Devices Power Dissipation 350 MHz1 400 MHz1,2 450 MHz1 Active3 Application Power AMD PowerNow! Technology Power Saving Mode4 Thermal Design Power (Maximum)5,6 Stop Grant/Halt (Maximum)6,7 VCC Nominal Stop Clock (Maximum)6,8 VCC Nominal Lowest Operating VCC9 5.60 W 6.90 W 2.95 W 7.50 W 9.50 W 2.50 W 1.60 W 1.30 W 8.70 W 12.00 W 1.90 W Notes: 1. This specification applies to components using a CLK frequency of 100 MHz. 2. This specification applies to components using a CLK frequency of 66 MHz. 3. The active application power measurements were taken by running a suite of embedded benchmarks covering four major embedded market segments: automotive, office automation, networking, and telecommunications. 4. AMD PowerNow! technology Power Saving Mode represents averaged values measured while running the processor in the lowest settings supported by AMD PowerNow! technology. 5. The maximum power dissipated in the normal clock control state must be taken into account when designing a solution for thermal dissipation for the AMD-K6-2E+ processor. 6. Maximum power is determined for the worst-case instruction sequence or function for the listed clock control states with VCC2 = Nominal VCC2 as listed in Table 55 on page 286 and VCC3 = 3.3 V. 7. The CLK signal and the internal PLL are still running, but most internal clocking has stopped. 8. The CLK signal, the internal PLL, and all internal clocking has stopped. 9. The lowest operating VCC is 1.4 V. Chapter 15 Electrical Data 289