Intel VC820 Design Guide - Page 111

Table 3-4. Trace Width Space Guidelines

|

View all Intel VC820 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 111 highlights

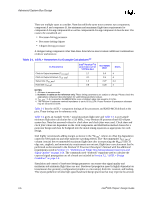

Advanced System Bus Design interference from AGTL+ signals in a particular group to AGTL+ signals in a different group. An example of AGTL+ to non-AGTL+ cross-talk is when CMOS and AGTL+ signals interfere with each other. Table 3-4. Trace Width Space Guidelines Cross-talk Type Intragroup AGTL+ (same group AGTL+) Intergroup AGTL+ (different group AGTL+) AGTL+ to non-AGTL+ Trace Width:Space Ratio 5:10 or 6:12 5:15 or 6:18 5:20 or 6:24 The spacing between the various bus agents causes variations in trunk impedance and stub locations. These variations cause reflections that can cause constructive or destructive interference at the receivers. A reduction of noise may be obtained by a minimum spacing between the agents. Unfortunately, tighter spacing results in reduced component placement options and lower hold margins. Therefore, adjusting the inter-agent spacing may be one way to change the network's noise margin, but mechanical constraints often limit the usefulness of this technique. Always be sure to validate signal quality after making any changes in agent locations or changes to inter-agent spacing. There are six AGTL+ signals that can be driven by more than one agent simultaneously. These signals may require more attention during the layout and validation portions of the design. When a signal is asserted (driven low) by two or more agents on the same clock edge, the two falling edge wave fronts will meet at some point on the bus and can sum to form a negative voltage. The ringback from this negative voltage can easily cross into the overdrive region. The signals are AERR#, BERR#, BINIT#, BNR#, HIT#, and HITM#. This document addresses AGTL+ layout for both 1 and 2-way 133 MHz/100 MHz processor/ Intel® 820 chipset systems. Power distribution and chassis requirements for cooling, connector location, memory location, etc., may constrain the system topology and component placement location; therefore, constraining the board routing. These issues are not directly addressed in this document. Section 1.2, "References" on page 1-2 contains a listing of several documents that address some of these issues. Intel®820 Chipset Design Guide 3-11