Intel VC820 Design Guide - Page 171

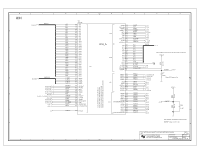

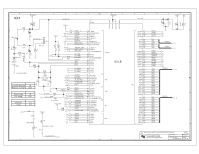

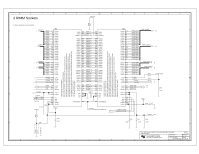

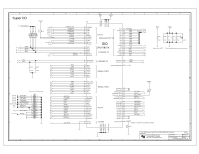

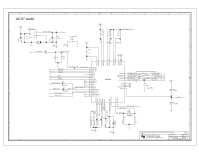

ICH_A, ICH

|

View all Intel VC820 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 171 highlights

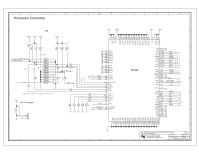

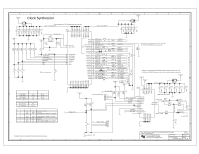

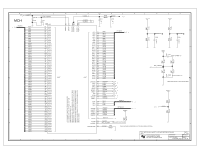

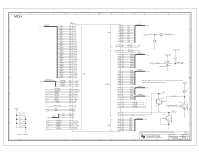

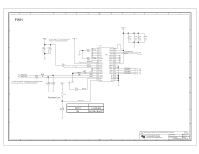

8 ICH D 7 16,20,21 AD[31:0] C 16,20,21 C_BE#[3:0] 16,20,21,32 16,20,21,32 16,20,21,32 16,20,21,32 B 16,20,21,32 16,20,21 6,10,11,12,16,19,20,21,22 20,21,32 16,20,21,32 16,20,21,32 16,19,20,21 21,32 21,32 5 A 8 7 6 5 AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 AD8 AD9 AD10 AD11 AD12 AD13 AD14 AD15 AD16 AD17 AD18 AD19 AD20 AD21 AD22 AD23 AD24 AD25 AD26 AD27 AD28 AD29 AD30 AD31 C_BE#0 C_BE#1 C_BE#2 C_BE#3 DEVSEL# FRAME# IRDY# TRDY# STOP# PAR PCIRST# PLOCK# SERR# PERR# PCI_PME# REQ#A GNT#A ICHPCLK U13 ICH_096 G2 AD0 G4 AD1 F2 AD2 F3 AD3 F4 AD4 F5 AD5 E1 AD6 E2 AD7 D1 AD8 D3 AD9 E4 AD10 C2 AD11 C1 AD12 B1 AD13' D4 AD14 C3 AD15 A4 AD16 B4 AD17 C5 AD18 C6 AD19 B5 AD20 E7 AD21 A6 AD22 B6 AD23 D7 AD24 B8 AD25 PCI A7 AD26 A8 AD27 B7 AD28 C9 AD29 D8 AD30 C7 AD31 D2 CBE0# B2 CBE#1 A3 CBE#2 D6 CBE#3 D9 DEVSEL# B3 FRAME# A2 IRDY# C4 TRDY# D5 STOP# A9 PAR J5 PCIRST# B9 PLOCK# A1 SERR# E9 PERR#/GPIO7 K1 PME# N6 GPIO0/REQ#A P5 GPIO16/GNT#A C14 PCICLK VCC1_8;G13,H14,K14,G15,L15,H16,J16 VCC3_3;C11,E13,N13,R13,M14,D16,T16 VCC3_3;E3,A5,E5,G5,N5,E6,P6,T7,C8,U10 GND;R2,G3,H8,J8,K8,H9,J9,K9,H10,J10,K10,G14,K15 4 3 2 1 CPU ICH_A HUB A20M# F13 CPUSLP# E12 FERR# F15 IGNNE# B17 INIT# E15 INTR E14 NMI B16 SMI# F14 STPCLK# A17 RCIN# A15 A20GATE B15 HL0 HL1 HL2 HL3 HL4 HL5 HL6 HL7 HL8 HL9 HL10 HL11 HL_STB HL_STB# HLCOMP HUBREF D17 E17 F17 G16 J15 K16 K17 L17 H15 J17 J14 F16 G17 H17 M17 J13 PIRQA# D10 PIRQB# A10 PIRQC# B10 PIRQD# C10 IRQ IRQ14 P11 IRQ15 N14 APICCLK C16 APICD0 E16 APICD1 C17 SERIRQ R4 REQ#0 A14 REQ#1 B13 REQ#2 B12 REQ#3 D12 REQ#4 B11 PCI GPIO1/REQ#B/REQ#5 P4 GNT#0 A13 GNT#1 C13 GNT#2 A12 GNT#3 C12 GNT#4 A11 GPIO17/GNT#B/GNT#5 R5 A20M# SLP# FERR# IGNNE# HINIT# LINT0 LINT1 SMI# STPCLK# KBRST# A20GATE HL0 HL1 HL2 HL3 HL4 HL5 HL6 HL7 HL8 HL9 HL10 HL11_TP HL_STB HL_STB# ICH_HLCOMP PIRQ#A PIRQ#B PIRQ#C PIRQ#D IRQ14 IRQ15 APICCLK PICD0 PICD1 SERIRQ PREQ#0 PREQ#1 PREQ#2 PREQ#3 PREQ#4 PREQ#5 PGNT#0 PGNT#1 PGNT#2 PGNT#3 PGNT#4 PGNT#5 4,32 4,32 4,32 4,32 4,10,32 4,32 4,32 4,32 4,32 12,32 12,32 HL[10:0] D 7 Place R239 less than 0.5" from the ICH using a 10 mil trace. VCC1_8 R239 40.2-1% TP1 C 7,37 7,37 HUBREF 6,8,37 16,19,20,21,32 19,20,21,32 20,21,32 20,21,32 C237 0.01UF Place C237 close to ICH. 22,32 22,32 5 4,32 4,32 12,21,32 VCC1_8 B 20,32 R225 301-1% 20,32 21,32 16,32 32 21,32 6,8,37 HUBREF R226 301-1% 20,32 20,32 21,32 16,32 32 21,32 C218 0.1UF Place HUBREF circuit between MCH and ICH HUBREF voltage = 0.9V +/- 2% A TITLE: INTEL(R) 820 CHIPSET CUSTOMER REFERENCE BOARD REV: ICH 1.01 R PCD PLATFORM DESIGN DRAWN BY: PROJECT: 1900 PRAIRIE CITY ROAD FOLSOM, CALIFORNIA 95630 LAST REVISED: SHEET: 11-24-1999_11:14 8 OF 36 6 5 4 3 2 1