Intel VC820 Design Guide - Page 214

No WD Reboot, Reboot on WD, Safe Mode, ICH strap, Normal, Clear, Strap

|

View all Intel VC820 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 214 highlights

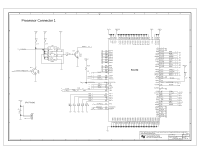

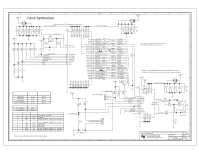

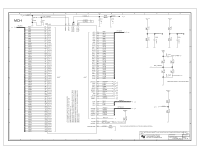

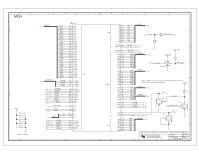

BAT17 CR3 C15 VCC5REF L1 VCCSUS1 N1 VCCSUS G1 VCCRTC BAT17 CR4 8 ICH 7 VCC3_3SBY 6 VCC_RTC_JP R245 D 1K VBAT_CR BAT17 CR5 R241 C- 8.2K A+ R250 VBAT_RC 1K C249 VBAT_RTC C BAT1 0.047UF 2 3 1 + Use CR2032 battery. S tra p B No W D Reboot Reboot on W D* S tra p S afe M ode ICH s trap* CM OS Norm al* Clear A C247 C246 2 1 2 1 + + 2.2UF 1UF +A -C VCC3_3 R233 1K RTC_RST_JP JP20 1 2 3 RTC_CLR VCC3_3 14 14 8.2K 8.2K R254 R317 31,33 32 9,18,31,33 20 27 19,33 7,14 20 R231 8.2K 3,5,13,34 3,5,13,34 34 R232 8.2K R247 10M C250 JP 26 IN OUT JP 5 IN OUT JP 20 1-2 2-3 12PF 12PF R249 10M Y4 XTAL 2 1 32.768KHZ C251 7 7 7 17 15,17 15,17 11,15,17 15,17 17 11,20 R215 8.2K R212 8.2K 7 23 PCI_TEST R98 20 0K 18,34 7 DRCG_CTRL R162 18,34 0K 12,14 VCC3_3SBY 12,14 12,14 12,14 R238 14 11,20 SPKR JP26 SPKR_STRAP 8.2K VCC3_3 2.7K 12,14 25 25 25 25 25 25 THRM# 3,5 SLP_S3# SLP_S5# PWROK PWRBTN# ICH_RI# RSMRST# MULT1_GPIO GPIO26_FPLED SMBDATA_CORE SMBCLK_CORE SMB_ALERT LPC_SMI# LPC_PME# INTRUDER# RTCRST# VBIAS RTCX1 RTCX2 ICH_CLK66 ICH_14MHZ ICH_48MHZ AC_RST# AC_SYNC AC_BITCLK AC_SDATAOUT AC_SDATAIN0 AC_SDATAIN1 SPKR GPIO12 GPIO13 GPIO21 MULT0_GPIO GPIO23_FPLED ALERTCLK_SBY ALERTDATA_SBY LAD0/FWH0 LAD1/FWH1 LAD2/FWH2 LAD3/FWH3 LDRQ#0 GPIO8 LFRAME#/FWH4 USBP1P USBP1N USBP0P USBP0N OC#1 OC#0 R341 R90 2.7K AC_SDOUT_STRAP JP5 5 U13 ICH_096 4 VCC3_3SBY D14 THRM# K3 GPIO24/SLP_S3# K2 SLP_S5# J3 PWROK M2 PWRBTN# L3 RI# F1 RSMRESET# L4 GPIO25/SUSSTAT# K4 SUSCLK/GPIO26 J1 SMBDATA J2 SMBCLK M1 GPIO11/SMBALERT# E11 GPIO6 D11 GPIO5 J4 GPIO10/INTRUDER# H1 RTCRST# H2 VBIAS H3 RTCX1 H4 RTCX2 A16 CLK66 U6 CLK14 U2 CLK48 T1 AC_RST# T3 AC_SYNC R3 AC_BIT_CLK T2 AC_SDOUT U1 ACSDIN0 P3 GPIO9/AC_SDIN1 U3 SPKR N4 GPIO12 L2 GPIO13 B14 GPIO21 D13 GPIO22 D15 GPIO23 M5 GPIO27/ALERT_CLK L5 GPIO28/ALERT_DATA R6 LAD0/FWH0 U5 LAD1/FWH1 T5 LAD2/FWH2 T4 LAD3/FWH3 T6 LDRQ0# N3 GPIO8/LDRQ1# U4 LFRAME#/FWH4 R1 USBP1+ P2 USBP1P1 USBP0+ N2 USBP0M4 OC1# M3 OC0# SYSTEM AC97 GPIO LPC USB ICH_B AC_SDATAOUT 11,15,17 8 7 6 5 4 3 VCC5_REF PDCS1# N12 SDCS1# L14 PDCS3# U13 SDCS3# L16 PDA0 PDA1 PDA2 SDA0 SDA1 SDA2 R12 T12 P12 M16 M15 L13 PDDREQ U11 SDDREQ P17 PDDACK# U12 SDDACK# M13 PDIOR# R11 SDIOR# N16 PDIOW# T11 SDIOW# N15 PIORDY N11 SIORDY N17 PDD0 R10 PDD1 N9 PDD2 R9 PDD3 U9 PDD4 R8 PDD5 U8 PDD6 R7 PDD7 U7 PDD8 P7 IDE PDD9 N7 PDD10 T8 PDD11 P8 PDD12 T9 PDD13 P9 PDD14 T10 PDD15 P10 SDD0 P15 SDD1 R16 SDD2 T17 SDD3 U16 SDD4 U15 SDD5 R14 SDD6 P13 SDD7 T13 SDD8 U14 SDD9 T14 SDD10 P14 SDD11 T15 SDD12 U17 SDD13 R15 SDD14 R17 SDD15 P16 2 C233 1 + C234 1UF 2 PDCS#1 SDCS#1 PDCS#3 SDCS#3 PDA0 PDA1 PDA2 SDA0 SDA1 SDA2 PDREQ SDREQ PDDACK# SDDACK# PDIOR# SDIOR# PDIOW# SDIOW# PIORDY SIORDY PDD0 PDD1 PDD2 PDD3 PDD4 PDD5 PDD6 PDD7 PDD8 PDD9 PDD10 PDD11 PDD12 PDD13 PDD14 PDD15 SDD0 SDD1 SDD2 SDD3 SDD4 SDD5 SDD6 SDD7 SDD8 SDD9 SDD10 SDD11 SDD12 SDD13 SDD14 SDD15 24 24 24 24 PDA[2:0] SDA[2:0] 24 24 24 24 24 24 24 24 24 24 PDD[15:0] SDD[15:0] 0.1UF 1 VCC3_3 VCC5 R230 1K +A -C D 24 24 C 24 B 24 A TITLE: INTEL(R) 820 CHIPSET DUAL PROCESSOR CUSTOMER REFERENCE BOARD REV: ICH 3.03 R PCD PLATFORM DESIGN DRAWN BY: PROJECT: 1900 PRAIRIE CITY ROAD FOLSOM, CALIFORNIA 95630 LAST REVISED: SHEET: 11-29-1999_14:46 11OF 38 3 2 1