Intel VC820 Design Guide - Page 173

Locked, Top Block Lock

|

View all Intel VC820 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 173 highlights

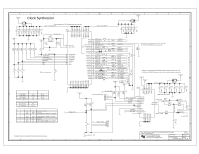

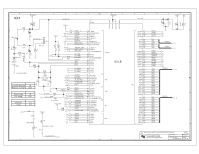

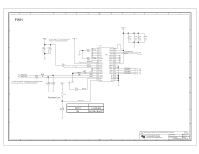

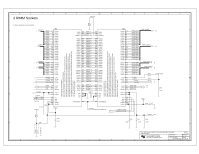

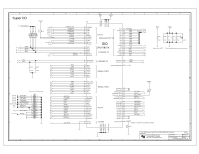

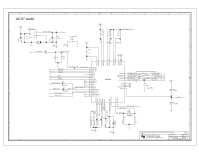

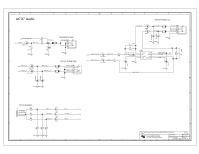

8 7 6 5 4 3 2 FWH D VCC3_3 Do not tie Vpp to 12V. Vpp should be tied to VCC3_3 for onboard programming. VCC3_3 C300 C305 0.1UF 0.1UF C 22 S66DETECT 22 P66DETECT R306 0K R305 0K For drive side detection, stuff R304,R307. No stuff R305,R306. For host side detection, stuff R304,R305,R306,R307. 5 R299 0K 6,8,11,12,16,19,20,21,22 R303 8.2K VCC3_3 VCC3_3 U16 R296 1 FWH_IC 2 8.2K 3 4 5 R298 6 FGPI4 7 8.2K 8 FWHPCLK 9 10 VPP_R 11 PCIRST# 12 13 14 R300 FGPI3 15 8.2K FGPI2 16 FGPI1 17 FGPI0 18 19 20 NC1 IC NC3 NC4 NC5 NC6 FGPI4 NC8 CLK VCC10 VPP RST# NC13 NC14 FGPI3 FGPI2 FGPI1 FGPI0 WP# TBL# GNDA 40 VCCA 39 FWH4 38 INIT# 37 FWH RFU36 36 RFU35 35 RFU34 34 RFU33 33 RFU32 32 VCC31 31 GND30 30 GND29 29 FWH3 28 FWH2 27 FWH1 26 FWH0 25 ID0 24 ID1 23 ID2 22 ID3 21 R307 15K R304 15K R308 4.7K WPROT B JP21 Top Block Lock TBLK_LCK R310 4.7K FW H OUT IN JP 21 Locked Unloc ked* VCC3_3 C301 C298 C297 C308 0.1UF 0.1UF 0.1UF 0.1UF LFRAME#/FWH4 HINIT# 9,12 4,8,32 LAD3/FWH3 9,12 LAD2/FWH2 9,12 LAD1/FWH1 9,12 LAD0/FWH0 9,12 1 D C B A A TITLE: INTEL(R) 820 CHIPSET CUSTOMER REFERENCE BOARD REV: FWH 1.01 R PCD PLATFORM DESIGN DRAWN BY: PROJECT: 1900 PRAIRIE CITY ROAD FOLSOM, CALIFORNIA 95630 LAST REVISED: SHEET: 11-18-1999_10:44 10 OF 36 8 7 6 5 4 3 2 1