Intel VC820 Design Guide - Page 39

Direct Rambus* Ground Plane Reference, Required

|

View all Intel VC820 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 39 highlights

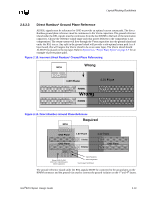

Layout/Routing Guidelines 2.6.2.3 Direct Rambus* Ground Plane Reference All RSL signals must be referenced to GND to provide an optimal current return path. The direct Rambus ground plane reference must be continuous to the Vterm capacitors. The ground reference island under the RSL signals must be continuous from the last RIMM to the back of the termination capacitors. Choose the reference island shape such that power delivery to the components is not compromised. The return current will flow through the Vterm capacitors into the ground island and under the RSL traces. Any split in the ground island will provide a sub-optimal return path. In a 4 layer board, this will require the Vterm island to be on an outer layer. The Vterm island should ALWAYS be placed on the top layer. Refer to Section 6.2, "Power Plane Splits" on page 6-7 for an example of power plane splits. Figure 2-15. Incorrect Direct Rambus* Ground Plane Referencing Wrong MCH 1.8V Plane RIMM1 Wrong RIMM2 3.3V Plane Figure 2-16. Direct Rambus Ground Plane Reference Required MCH GND Plane GND Plane 1.8V Plane RIMM1 RIMM2 3.3V Plane GND Plane Extend GND PLANE Reference Island Beyond Vterm Capacitors Vterm Resistors Vterm Capacitors Vterm Layer Not Shown The ground reference island under the RSL signals MUST be connected to the ground pins on the RIMM connector and the ground vias used to connect the ground isolation on the 1st and 4th layers. Intel®820 Chipset Design Guide 2-13