Intel VC820 Design Guide - Page 121

Reference Planes and PCB Stackup

|

View all Intel VC820 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 121 highlights

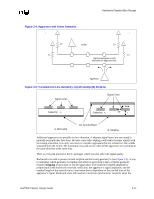

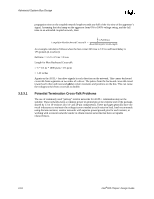

Advanced System Bus Design change the impedance of adjacent trace layers. (For instance, the impedance calculations may have been done for microstrip geometry, and adding a partial plane on the other side of the trace layer may turn the microstrip into a stripline.) 3.4.3.2 Reference Planes and PCB Stackup It is strongly recommended that baseboard stackup be arranged such that AGTL+ signals are referenced to a ground (VSS) plane, and that the AGTL+ signals do not traverse multiple signal layers. Deviating from either guideline can create discontinuities in the signal's return path that can lead to large SSO effects that degrade timing and noise margin. Designing an AGTL+ platform incorporating discontinuities will expose the platform to a risk that is very hard to predict in prelayout simulation. Figure 3-6 shows the ideal case where a particular signal is routed entirely within the same signal layer, with a ground layer as the single reference plane. Figure 3-6. One Signal Layer and One Reference Plane Signal Layer A Ground Plane 1lay 1ref plane vsd When it is not possible to route the entire AGTL+ signal on a single VSS referenced layer, there are methods to reduce the effects of layer switches. The best alternative is to allow the signals to change layers while staying referenced to the same plane (see Figure 3-7). Figure 3-8 shows another method of minimizing layer switch discontinuities, but may be less effective than Figure 3-7. In this case, the signal still references the same type of reference plane (ground). In such a case, it is important to stitch (i.e., connect) the two ground planes together with vias in the vicinity of the signal transition via. Figure 3-7. Layer Switch with One Reference Plane Signal Layer A Ground Plane Signal Layer B l 1 fl d Figure 3-8. Layer Switch with Multiple Reference Planes (same type) Signal Layer A Ground Plane Layer Layer Ground Plane Signal Layer B l M lt f l d Intel®820 Chipset Design Guide 3-21