Intel VC820 Design Guide - Page 32

Data Strobing Example, Effect of Crosstalk on Strobe Signal

|

View all Intel VC820 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 32 highlights

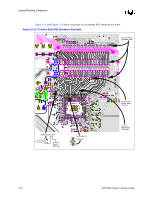

Layout/Routing Guidelines Figure 2-6. Data Strobing Example Data Sample Clock Strobe Data data_str.vsd For a source synchronous strobed interface, it is very important that the strobe signals are routed carefully. These signals must be very clean (free of noise). Data signals are typically latched on the rising or falling edge of the strobe signal (or both). If there is noise on these signals, it could cause an extra "edge" to be detected, thus latching incorrect data. Refer to Figure 2-7 for examples. Figure 2-7. Effect of Crosstalk on Strobe Signal a) Correct Strobing Example (no noise) b) Effect of Crosstalk on Strobe Signal clock Data Data is correctly latchecd as a "0" clock Data Data is incorrectly latchecd as a "1" Noise (i.e., crosstalk) Threshold Threshold Strobe Strobe Some buses have more than one strobe (i.e., AGP). The AGP 1.0 specification (1X and 2X mode) employs 3 strobe signals. These three strobe signals are each used to strobe different data signals. That is, each strobe has an associated set of data signals. The associations for AGP 1.0 (AGP 2X) are documented in Table 2-1. Refer to Section 2.7, "AGP 2.0" on page 2-31 for more information on AGP 2.0 (AGP 4X, 1.5v). Table 2-1. AGP 2X Data/Strobe Association Data Associated Strobe AD[15:0] and C/BE[1:0]# AD[31:16] and C/BE[3:2]# SBA[7:0] AD_STB0 AD_STB1 SB_STB In this example, the lower address signals (AD[15:0]) are sampled on the rising and falling edges of AD_STB0, while the upper address signals (AD[31:16]) are sampled on the rising and falling edges of AD_STB1. 2-6 Intel®820 Chipset Design Guide