Intel VC820 Design Guide - Page 210

BUS/RAMBUS, Sprd Spect, GPO CNTRL, Enabled, Disabled

|

View all Intel VC820 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 210 highlights

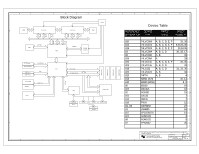

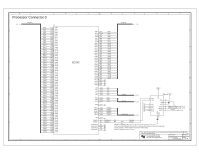

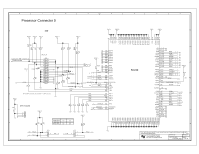

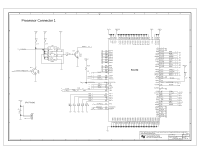

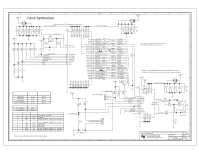

8 7 6 5 4 3 2 VCC2_5 VCC3_3 Clock Synthesizer L20 1 2 FBHS01L Provide at least one 0.1uF decoupling cap per power pin. VCC_3_3_CK133_FB VCC2_5_CK133_FB L21 1 2 FBHS01L C180 C190 C192 C199 C171 C207 C215 C223 C186 C198 C206 C214 C170 D U11 CK133 1 D 0.1UF 0.1UF 0.1UF 0.1UF 10UF VDD3V_1 4 VDD3V_2 10 VDD3V_3 16 VDD3V_4 23 VDD3V_5 27 VDD3V_6 39 VDD3V_7 31 VDD25V_1 56 VDD25V_2 51 VDD25V_3 47 VDD25V_4 43 0.1UF 0.1UF 0.1UF 0.1UF 0.1UF 0.1UF 0.1UF 10UF R206 10K R203 10K R202 10K R197 10K R196 10K R192 10K R224 VCC3_3 C JP17 JP15 JP14 Y3 XTAL CK133_XIN VCC3_3 1 2 14.318MHZ C185 CK133_XOUT C189 10PF 10PF 220 5 XTAL_IN 6 XTAL_OUT 4,6,9 SEL133/100# PCISTOP# CPUSTOP# CK133_PWRDWN# SPREAD# SEL1 SEL0 28 SEL133/100# 37 PCISTOP# 36 CPUSTOP# 35 PWRDWN# 34 SPREAD# 33 SEL1 32 SEL0 2_5V APIC0 APIC1 APIC2 CPU_DIV2_1 CPU_DIV2_2 CPUCLK0 CPUCLK1 CPUCLK2 CPUCLK3 PCICLK_F PCICLK1 PCICLK2 PCICLK3 PCICLK4 PCICLK5 PCICLK6 PCICLK7 3V66_0 3V66_1 3V66_2 3V66_3 48MHZ REF0 REF1 53 PICCLK_R R155 22 54 APICCLK_R 22 55 PICCLK1_R 22 50 CPU_DIV2_1_R R151 22 R156 R148 PICCLK APICCLK PICCLK1 CPU_DIV2 4 10 6 49 CPU_DIV2_2_R 41 ITPCLK_R R188 22 42 CPUHCLK_R 22 R189 45 22 R184 ITPCLK MCHCLK CPUHCLK 46 CPUHCLK1_R R170 22 CPUHCLK1 4 8 4,6 6 8 ICHPCLK_R R165 33 9 PCLK1_R 11 PCLK2_R R169 33 12 PCLK3_R 14 PCLK4_R R186 33 15 PCLK5_R 17 FWHPCLK_R R191 33 18 SIO_PCLK7_R 21 MCH_CLK66_R33 R201 22 25 ICH_CLK66_RR210 33 26 TEST_CLK66_R 30 IHC_48MHZ_RR221 22 2 IHC_14MHZ_R 3 SIO_14MHZ_RR150 22 R164 33 R183 33 R187 33 R194 33 R195 33 R211 33 R147 22 ICHPCLK 10 PCLK1 22 PCLK2 22 PCLK3 23 PCLK4 23 PCLK5 18 FWHPCLK 12 SIO_PCLK7 14 AGPCLK_CONN 21 MCH_CLK66 9 ICH_CLK66 11 TEST_CLK66 ICH_48MHZ 11 ICH_14MHZ 11 SIO_14MHZ 14 VCC3_3 No stuff R106 for debug. VCC1_8 R220 33 R166 30 Keep stubs on unused outputs as short as possible. Tie CPUCLK and MCHCLK outputs together. C VDDIR pin on DRCG should be decoupled at the component with a 0.1uF cap. CLKTM and CLKTM# RC network must use 5% or better tolerance components. VCC3_3 VCC2_5 VCC1_8 L22 1 2 VCC3_3_DRCG_FB FBHS01L 1 VSS1 7 VSS2 13 VSS3 19 VSS4 20 VSS5 24 VSS6 52 VSS7 48 VSS8 44 VSS9 40 VSS10 38 VSS11 29 VSS12 U12 DRCG C208 C196 C204 C220 C209 0.1UF 0.1UF 0.1UF 0.1UF 10UF VDDIR 1 VDDIPD 10 VDDO1 16 VDDO2 22 VDDP 3 VDDC 9 R219 10K R204 10K R199 10K B HOST BUS /RAM BUS JP 13 100/300 2 -3 100/400 OUT 133/400 2 -3 G P O CNTRL* 1 -2 JP 18 OUT OUT OUT OUT VCC3_3 MULT0_GPIO 11 JP13 is for debug only. JP13 1 2 3 R161 10K R217 10K S prd S pe ct E nabled* D is abled JP 14 IN OUT S EL133/ 100# 0 0 0 JP15 IN IN OUT JP 17 IN OUT IN Function All outputs Tri-State Res erved Active 100MHz, 48MHz PLL inactive A 0 OUT OUT Active 100MHz, 48MHz PLL active 1 IN IN Test Mode 1 IN OUT Reserved 1 OUT IN Active 133MHz,48MHz PLL inactive 1 OUT OUT Active 133MHz,48MHz PLL active* All jumpers may not be required, but are included for test purposes. 11 DRCG_CTRL JP11 11,14 MULT1_GPIO JP18 1 2 3 No stuff R161, JP11. 8 7 6 5 4 0.1UF 4PF DRCG_PWRDWN# STOPB# MULT0 MULT1 HCLKOUT 9 RCLKOUT 9 2 REFCLK 12 PWRDN# 11 STOPB# 15 MULT0 14 MULT1 24 S0 23 S1 13 GND 6 PCLKM 7 SYNCLKN 19 NC 17 GNDO1 21 GNDO2 4 GNDP 8 GNDC 5 GNDI B CLK CLKB# 39-1% DRCG_CLK R182 20 51-1% 18 R185 CLKTM 51-1% R200 13 C80 CLKTM_RD 39-1% DRCG_CLKB# R205 CLKTM# 13 No stuff C80 C205 A TITLE: INTEL(R) 820 CHIPSET DUAL PROCESSOR CUSTOMER REFERENCE BOARD REV: CLOCK SYNTHESIZER 3.03 R PCD PLATFORM DESIGN DRAWN BY: PROJECT: 1900 PRAIRIE CITY ROAD FOLSOM, CALIFORNIA 95630 LAST REVISED: SHEET: 11-29-1999_14:46 7 OF 38 3 2 1