Intel VC820 Design Guide - Page 116

Timing Requirements, 3.3.3 Cross-talk Theory,

|

View all Intel VC820 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 116 highlights

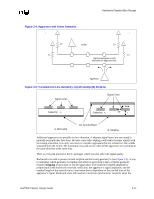

Advanced System Bus Design 3.3.2 3.3.3 Timing Requirements The system timing for AGTL+ is dependent on many things. Each of the following elements combine to determine the maximum and minimum frequency the AGTL+ bus can support: • The range of timings for each of the agents in the system. - Clock to output [TCO]. (Note that the system load is likely to be different from the "specification" load therefore the TCO observed in the system might not be the same as the TCO from the specification.) - The minimum required setup time to clock [TSU_MIN] for each receiving agent. • The range of flight time between each component. This includes: - The velocity of propagation for the loaded printed circuit board [SEFF]. - The board loading impact on the effective TCO in the system. • The amount of skew and jitter in the system clock generation and distribution. • Changes in flight time due to cross-talk, noise, and other effects. Cross-talk Theory AGTL+ signals swing across a smaller voltage range and have a correspondingly smaller noise margin than technologies that have traditionally been used in personal computer designs. This requires that designers using AGTL+ be more aware of cross-talk than they may have been in past designs. Cross-talk is caused through capacitive and inductive coupling between networks. Cross-talk appears as both backward cross-talk and as forward cross-talk. Backward cross-talk creates an induced signal on a victim network that propagates in a direction opposite that of the aggressor's signal. Forward cross-talk creates a signal that propagates in the same direction as the aggressor's signal. On the AGTL+ bus, a driver on the aggressor network is not at the end of the network; therefore it sends signals in both directions on the aggressor's network. Figure 3-4 shows a driver on the aggressor network and a receiver on the victim network that are not at the ends of the network. The signal propagating in each direction causes cross-talk on the victim network. 3-16 Intel®820 Chipset Design Guide