Intel VC820 Design Guide - Page 130

Intel, Chipset Platform Clock Distribution

|

View all Intel VC820 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 130 highlights

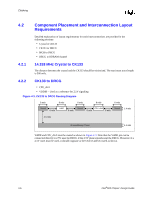

Clocking • The MCH hub interface/AGP clock and the ICH hub interface clock. The DRCG reference clock operates at one-half the CPU clock frequency. It is an input into the DRCG and is used to generate the Direct RDRAM "Clock to Master" differential pair (CTM, CTM#). The DRCG generates one pair of differential Direct RDRAM Clocks (CTM, CTM#) from the reference clock generated by the CK133. In addition, the DRCG uses phase information provided by the MCH to phase align the direct RDRAM clock with the CPU clocks. This phase alignment information is provided to the DRCG via the SYNCLKN and PCLKM pins. Figure 4-1. Intel® 820 Chipset Platform Clock Distribution CPUCLK APIC CPUCLK APIC CPUCLK 3V66 CPU_DIV2 3V66 APIC PCICLK* 3V66 CK133 REF 48Hz PCICLK PCICLK PCICLK Processor A CLK B PICCLK Processor C CLK D PICCLK RDRAM RCLK TCLK RDRAM RCLK TCLK RDRAM RCLK TCLK RDRAM TERM RCLK TCLK MCH CTM CFM E F HCLKIN CLK66 PHASEINFO G APICCLK ICH H PCICLK I CLK66 J CLK14 K CLK48 L CLK PCI SLOTS L CLK PCI SLOTS L CLK PCI SLOTS L CLK PCI SLOTS PHASEINFO Q REFCLK DRCG P CLK AGP CONNECTOR N CLK FWH Flash BIOS M CLK LPC * The free-running PCI clock should be connected to the ICH. 4-2 Intel®820 Chipset Design Guide