Intel VC820 Design Guide - Page 37

RSL Termination, Secondary Side RSL Breakout Example - ram

|

View all Intel VC820 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 37 highlights

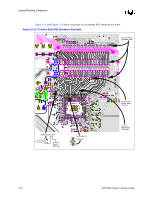

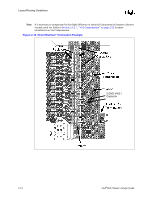

Figure 2-12. Secondary Side RSL Breakout Example Layout/Routing Guidelines 2.6.2.2 RSL Termination All RSL signals must be terminated to 1.8V (Vterm) using 27Ω-2% or 28Ω-1% resistors at the end of the channel opposite the MCH. Resistor packs are acceptable. Vterm must be decoupled using high speed bypass capacitors (one 0.1 µF ceramic chip capacitor per two RSL lines) near the terminating resistors. Additionally, bulk capacitance is required. Assuming a linear regulator with approximate 20 ms response time, two 100 µF tantalum capacitors are recommended. The trace length between the last RIMM and the termination resistors should be less than 3". Length matching in this section of the channel is not required. The Vterm power island should be at LEAST 50 mils wide. This voltage does not need to be supplied during suspend-to-RAM. Figure 2-13. Direct RDRAM Termination Terminator R-packs RSL Signals Vterm Intel®820 Chipset Design Guide 2-11