Intel VC820 Design Guide - Page 211

Title: Intelr 820 Chipset Dual Processor Customer Reference Board

|

View all Intel VC820 manuals

Add to My Manuals

Save this manual to your list of manuals |

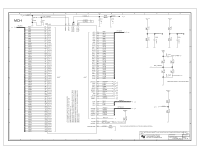

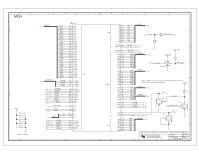

Page 211 highlights

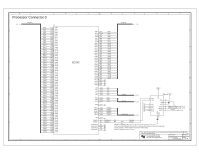

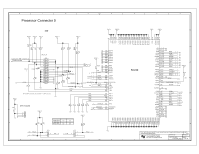

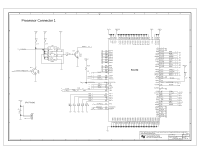

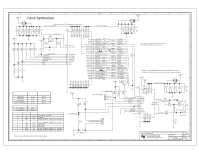

8 10 MCH HUBREF C194 21 0.01UF 3,5 D HD#[63:0] C B A HD#0 HD#1 HD#2 HD#3 HD#4 HD#5 HD#6 HD#7 HD#8 HD#9 HD#10 HD#11 HD#12 HD#13 HD#14 HD#15 HD#16 HD#17 HD#18 HD#19 HD#20 HD#21 HD#22 HD#23 HD#24 HD#25 HD#26 HD#27 HD#28 HD#29 HD#30 HD#31 HD#32 HD#33 HD#34 HD#35 HD#36 HD#37 HD#38 HD#39 HD#40 HD#41 HD#42 HD#43 HD#44 HD#45 HD#46 HD#47 HD#48 HD#49 HD#50 HD#51 HD#52 HD#53 HD#54 HD#55 HD#56 HD#57 HD#58 HD#59 HD#60 HD#61 HD#62 HD#63 7 CONN_AGPREF C155 0.1UF U10 MCH_096 R2 R1 R4 P5 T1 R5 V1 Y2 W1 U1 T2 Y3 W2 U3 Y1 U2 W4 W3 V4 U4 T3 Y4 Y5 T4 V5 T5 Y6 W5 U6 V6 W6 T6 W7 U7 Y8 Y7 T8 W8 T7 W9 U8 W10 Y10 V8 U9 Y9 W11 T9 Y11 T10 T12 U10 V10 W12 T11 U13 Y13 Y12 W14 U11 U12 Y14 V14 W13 HD#0 HD#1 HD#2 HD#3 HD#4 HD#5 HD#6 HD#7 HD#8 HD#9 HD#10 HD#11 HD#12 HD#13 HD#14 HD#15 HD#16 HD#17 HD#18 HD#19 HD#20 HD#21 HD#22 HD#23 HD#24 HD#25 HD#26 HD#27 HD#28 HD#29 HD#30 HD#31 HD#32 HD#33 HD#34 HD#35 HD#36 HD#37 HD#38 HD#39 HD#40 HD#41 HD#42 HD#43 HD#44 HD#45 HD#46 HD#47 HD#48 HD#49 HD#50 HD#51 HD#52 HD#53 HD#54 HD#55 HD#56 HD#57 HD#58 HD#59 HD#60 HD#61 HD#62 HD#63 6 HOST 8 7 6 VCC1_8;D4,E6,F6,G6,E7,R6,R7,E8,E9,D10,D11,E12 VCC1_8;E13,E14,F14,T14,E15,P15,B17,C17,C19 VDDQ;F15,R15,J17,L17,N17,T17 GND;A1,A3,G3,J3,L3,N3,R3,V3,B4,D5,L5,U5,B6,D6,D7,V7,B8,D8 GND;D9,J9,K9,L9,M9,V9,B10,J10,K10,L10,M10,C11,J11,K11,L11 GND;M11,V11,C12,D12,J12,K12,L12,M12,B13,D13,V13,T13,D14 GND;B15,D15,B16,D16,E16,F16,A17,E18,V18,A19,H19,K19,M19 GND;P19,T19,D20 C3 GTLREFA V12 GTLREFB E11 RAMREFA E10 RAMREFB U14 AGPREF E20 HUBREF 5 4 3 RAMREF_R GTLREF2 8 R168 RAMREF 8,13 100-1% C191 C203 GTLREF1 8 2 VTT1_5 1 VTT1_5 0.1UF 0.1UF R143 75-1% R131 75-1% HOST HA#3 J1 HA#4 H3 HA#5 H4 HA#6 G5 HA#7 K2 HA#8 H5 HA#9 H2 HA#10 J4 HA#11 L1 HA#12 J5 HA#13 K1 HA#14 J2 HA#15 K5 HA#16 K3 HA#17 L4 HA#18 K4 HA#19 L2 HA#20 N2 HA#21 M3 HA#22 M2 HA#23 M1 HA#24 N5 HA#25 M4 HA#26 P1 HA#27 N1 HA#28 P2 HA#29 P3 HA#30 N4 HA#31 M5 CPURST# P4 ADS# D2 BNR# F5 BPRI# G1 DBSY# D1 DEFER# F2 DRDY# F1 HIT# D3 HITM# E1 HLOCK# F3 HTRDY# F4 RS#0 E5 RS#1 C1 RS#2 E2 HREQ#0 H1 HREQ#1 G4 HREQ#2 E4 HREQ#3 E3 HREQ#4 G2 HCLKIN V2 RSTIN# F20 HLCOMP A18 TEST/GRCOMP T15 HA#3 HA#4 HA#5 HA#6 HA#7 HA#8 HA#9 HA#10 HA#11 HA#12 HA#13 HA#14 HA#15 HA#16 HA#17 HA#18 HA#19 HA#20 HA#21 HA#22 HA#23 HA#24 HA#25 HA#26 HA#27 HA#28 HA#29 HA#30 HA#31 HA#[31:0] 3,5 R130 150-1% R149 1K-1% C182 R153 80.6-1% GTLREF2 C158 D GTLREF1 C183 R144 150-1% 0.001UF 0.001UF VDDQ C187 470PF MCH_AGPREF_CV R160 80.6-1% R154 1K-1% C MCH_AGPREF 21 470PF MCH_AGPREF_CG CPURST# HADS# BNR# BPRI# DBSY# DEFER# DRDY# HIT# HITM# HLOCK# HTRDY# RS#0 RS#1 RS#2 HREQ#0 HREQ#1 HREQ#2 HREQ#3 HREQ#4 4,6 4,6 4,6 4,6 4,6 4,6 4,6 4,6 4,6 4,6 4,6 RS#[2:0] 3,5 HREQ#[4:0] 3,5 VCC1_8 R181 562-1% R190 162-1% Place MCH_AGPREF circuit near the MCH. VCC1_8 B RAMREF 8,13 R180 40.2-1% MCHCLK 7 PCIRST# 10,12,13,14,18,21,22,23,24 MCH_HLCOMP A GRCOMP R129 40.2-1% Place R129 and R180 less than 0.5" from MCH using 10 mil trace. 5 4 TITLE: INTEL(R) 820 CHIPSET DUAL PROCESSOR CUSTOMER REFERENCE BOARD REV: MCH 3.03 R PCD PLATFORM DESIGN DRAWN BY: PROJECT: 1900 PRAIRIE CITY ROAD FOLSOM, CALIFORNIA 95630 LAST REVISED: SHEET: 11-30-1999_10:02 8 OF 38 3 2 1