Intel VC820 Design Guide - Page 170

Intel VC820 - Desktop Board Motherboard Manual

|

View all Intel VC820 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 170 highlights

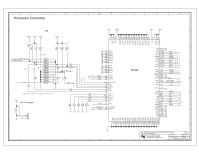

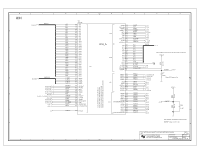

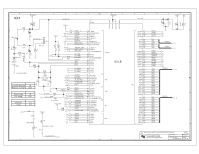

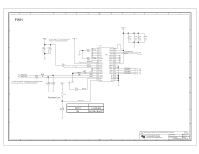

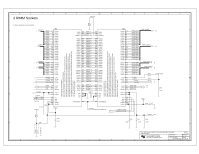

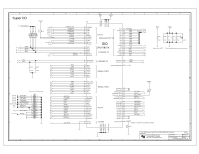

8 MCH D C B VCC1_8 0.1UF 0.1UF 0.1UF A 0.1UF No stuff. For test only. 8 C362 C360 C359 C361 7 6 5 GAD[31:0] 19 GC/BE#[3:0] 19 GAD0 GAD1 GAD2 GAD3 GAD4 GAD5 GAD6 GAD7 GAD8 GAD9 GAD10 GAD11 GAD12 GAD13 GAD14 GAD15 GAD16 GAD17 GAD18 GAD19 GAD20 GAD21 GAD22 GAD23 GAD24 GAD25 GAD26 GAD27 GAD28 GAD29 GAD30 GAD31 GC/BE#0 GC/BE#1 GC/BE#2 GC/BE#3 19,32 19,32 19,32 19,32 19,32 19,32 19,32 19,32 19,32 5 19,32 19,32 19 19,32 19,32 19,32 19,32 19,32 19,32 GFRAME# GDEVSEL# GIRDY# GTRDY# GSTOP# GPAR GREQ# GGNT# PIPE# MCH_CLK66 RBF# WBF# ST0 ST1 ST[2:0] ST2 ADSTB0 ADSTB#0 ADSTB1 ADSTB#1 SBSTB SBSTB# U10 MCH_096 F17 G_AD0 G18 G_AD1 G17 G_AD2 G19 G_AD3 G16 G_AD4 G20 G_AD5 H17 G_AD6 H18 G_AD7 J20 G_AD8 J16 G_AD9 K17 G_AD10 K18 G_AD11 J18 G_AD12 L19 G_AD13 K20 G_AD14 L18 G_AD15 M17 G_AD16 P18 G_AD17 M16 G_AD18 P17 G_AD19 N16 G_AD20 P20 G_AD21 P16 G_AD22 R20 G_AD23 T20 G_AD24 R17 G_AD25 U17 G_AD26 T16 G_AD27 U18 G_AD28 T18 G_AD29 U20 G_AD30 U19 G_AD31 H16 G_C/BE#0 L20 G_C/BE#1 N18 G_C/BE#2 R16 G_C/BE#3 L16 N19 N20 M20 M18 K16 U15 Y16 W16 G_FRAME# G_DEVSEL# G_IRDY# G_TRDY# G_STOP# G_PAR G_REQ# G_GNT# PIPE# W18 CLK66 V16 RBF# V15 WBF# W15 ST0 Y15 ST1 Y17 ST2 J19 AD_STB0 H20 AD_STB#0 R18 AD_STB1 R19 AD_STB#1 Y20 SB_STB Y19 SB_STB# AGP 7 6 5 4 3 2 1 HUB MEMORY AGP HL0 F19 HL1 F18 HL2 E17 HL3 E19 HL4 B20 HL5 B19 HL6 B18 HL7 A20 HL8 D17 HL9 C18 HL10 D18 HL_STB D19 HL_STB# C20 RCLKOUT B1 HCLKOUT A2 DQA0 A13 DQA1 C13 DQA2 A14 DQA3 C14 DQA4 B14 DQA5 C15 DQA6 A15 DQA7 C16 DQA8 A16 DQB0 C7 DQB1 B7 DQB2 C6 DQB3 A6 DQB4 C5 DQB5 A5 DQB6 B5 DQB7 A4 DQB8 C4 RQ0 A7 RQ1 C8 RQ2 A8 RQ3 C9 RQ4 B9 RQ5 A9 RQ6 A10 RQ7 C10 CTM B11 CTM# A11 CFM A12 CFM# B12 CMD B3 SCK B2 SIO C2 SBA0 SBA1 SBA2 SBA3 SBA4 SBA5 SBA6 SBA7 W20 V17 Y18 W17 V20 W19 V19 U16 4 HL[10:0] HL0 8 HL1 HL2 HL3 D HL4 HL5 HL10 R209 SEL133/100# HL6 7,8,37 4,5 8.2K HL7 HL8 HL9 HL10 R227 8.2K HL_STB 8,37 HL_STB# 8,37 RCLKOUT HCLKOUT LDQA0 LDQA1 LDQA2 LDQA3 LDQA4 LDQA5 LDQA6 LDQA7 LDQA8 5 5 LDQA[8:0] VCC3_3SBY 11 VCC3_3SBY 14 R248 4.7K 9,16,29,31 PWROK U14 VCC 13 12 GND SN74LVC07A PWROK_CTRL C 7 7 MMBT3904LT1 LDQB0 LDQB1 LDQB2 LDQB3 LDQB4 LDQB5 LDQB6 LDQB7 LDQB8 LDQB[8:0] 11 LSCK and LCMD must neck down to 5 mils for 175 mils at Q10 and Q9 attach points. Place Q10 and Q9 as close as possible to MCH. VCC5SBY LCOL[4:0] LCOL0 11 LCOL1 LCOL2 LCOL3 LCOL4 LROW[2:0] LROW0 11 LROW1 LROW2 LCLKTM 11 LCLKTM# 11 LCLKFM 11 LCLKFM# 11 LSCK 11 4.7K B C Q10 SCK_CTRL 3 1B 2 E 7 Q14 C 3 PWROK_CTRL B 1 2 MMBT3904LT1 E LCMD 11 R346 LSIO SBA0 SBA1 SBA2 SBA3 SBA4 SBA5 SBA6 SBA7 3 MMBT3904LT1 SBA[7:0] 11 19 Q9 C 3 B1 2 E A TITLE: INTEL(R) 820 CHIPSET CUSTOMER REFERENCE BOARD MCH R PCD PLATFORM DESIGN DRAWN BY: 1900 PRAIRIE CITY ROAD FOLSOM, CALIFORNIA 95630 LAST REVISED: 11-18-1999_11:34 2 1 REV: 1.01 PROJECT: SHEET: 7 OF 36