Intel VC820 Design Guide - Page 35

RSL Routing Dimensions, Table 2-2. Placement Guidelines for Motherboard Routing Lengths

|

View all Intel VC820 manuals

Add to My Manuals

Save this manual to your list of manuals |

Page 35 highlights

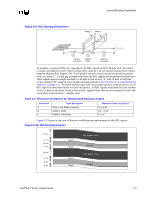

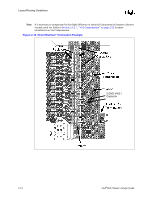

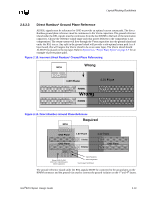

Layout/Routing Guidelines Figure 2-9. RSL Routing Dimensions RIMM_0 RIMM_1 MCH 0"-3.50" A 0.4"-0.45" B MCH to RIMM to First RIMM RIMM 0"-3" C RIMM to Termination To maintain a nominal 28 Ω trace impedance, the RSL signals must be 18 mils wide. To control crosstalk and odd/even mode velocity deltas, there must be a 10 mil ground isolation trace routed between adjacent RSL signals. The 10 mil ground isolation traces must be connected to ground with a via every 1". A 6 mil gap is required between the RSL signals and the ground isolation trace. These signals must be length matched to ±10 mils in line section "A" and ±2 mils in both line sections labeled "B" using the trace length matching methods in Section 2.6.2.6, "Length Matching Methods" on page 2-21. To ensure uniform trace lines, trace width variation must be uniform on all RSL signals at every neck-down for each line section. All RSL signals must have the same number of vias. It may be necessary to place vias on RSL signals where they are not necessary to meet this via loading requirement (i.e., dummy vias). Table 2-2. Placement Guidelines for Motherboard Routing Lengths Reference Trace Description Maximum Trace Length (in.) A MCH to first RIMM Connector B RIMM to RIMM C RIMM to Termination 0" to 3.50" 0.4" - 0.45" 0" to 3" Figure 2-10 shows a top view of the trace width/spacing requirements for the RSL signals. Figure 2-10. RSL Routing Diagram 18 mils 6 mils 10 mils 6 mils 18 mils 6 mils 10 mils 6 mils Space Space Space Space RSL Signal Trace Ground RSL Signal Trace Ground Intel®820 Chipset Design Guide 2-9